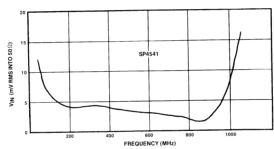

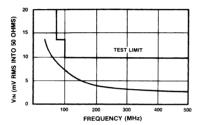

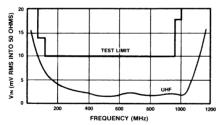

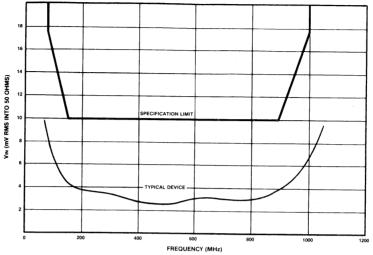

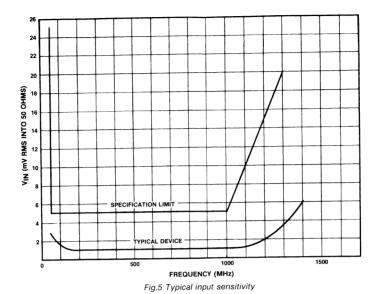

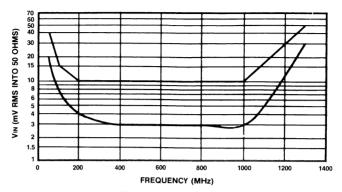

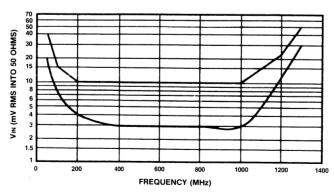

800 1200 1600 FREQUENCY (MHz)

SATELLITE, CABLE AND TV INTEGRATED CIRCUIT HANDBOOK

© The Plessey Company plc 1986 Publication No. P.S.1973 May 1986

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to be reproduced or to form part of any order or contract or to be regarded as a representation relating to the products or services concerned. Any applications of products shown in this publication are for illustration purposes only and do not give or imply any licences or rights to use the information for any purposes whatsoever. It is the responsibility of any person who wishes to use the application information to obtain any necessary licence for such use. We reserve the right to alter without notice the specification, design, price or conditions of supply of any product or service. PLESSEY, the Plessey symbol and PLESSEY MEGACELL are registered trademarks of The Plessey Company plc.

## **Contents**

|                                     | Page |

|-------------------------------------|------|

| Product index                       | 5    |

| Selection guide                     | . 7  |

| The quality concept                 | 9    |

| Screening to BS9400                 | 10   |

| Plessey Hi-Rel screening            | 11   |

| Semi-custom design                  | 12   |

| Plessey Megacell                    | 13   |

| Thermal design                      | 14   |

| Plessey ICs for Satellite reception | 16   |

| Technical data                      | 19   |

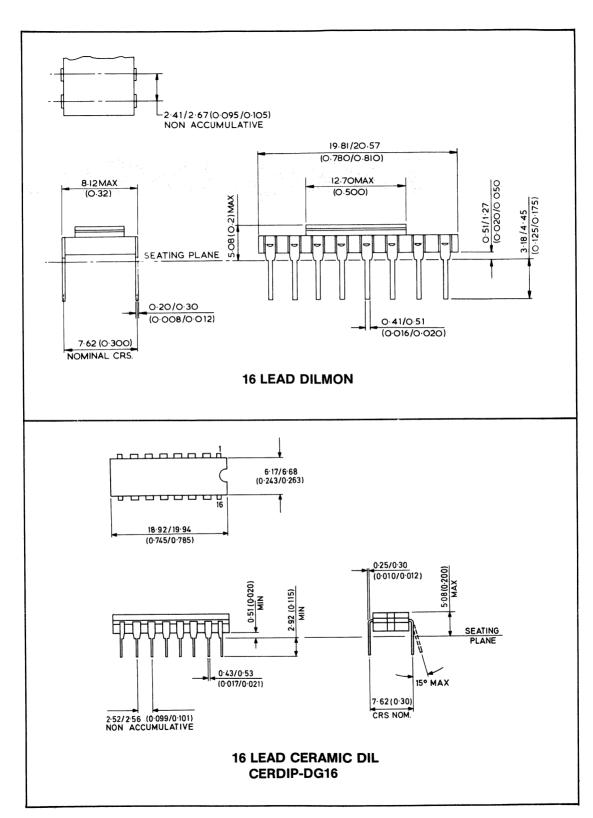

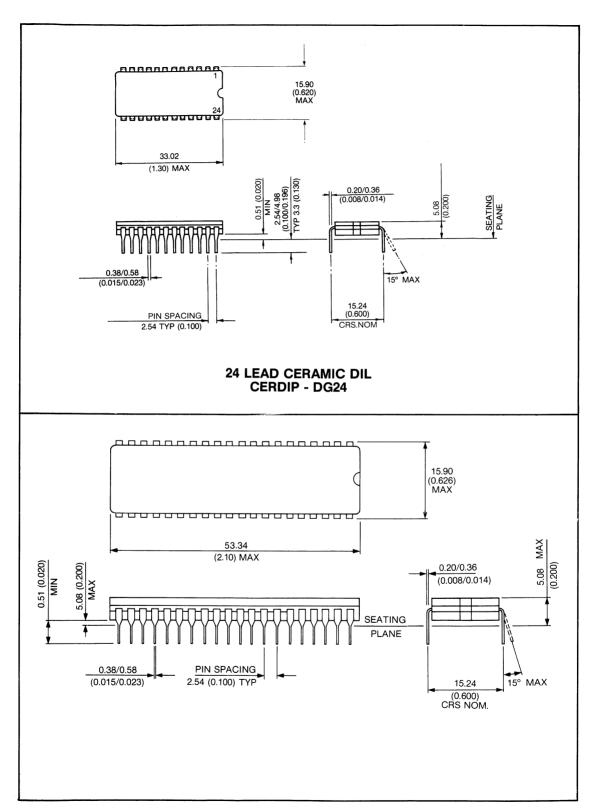

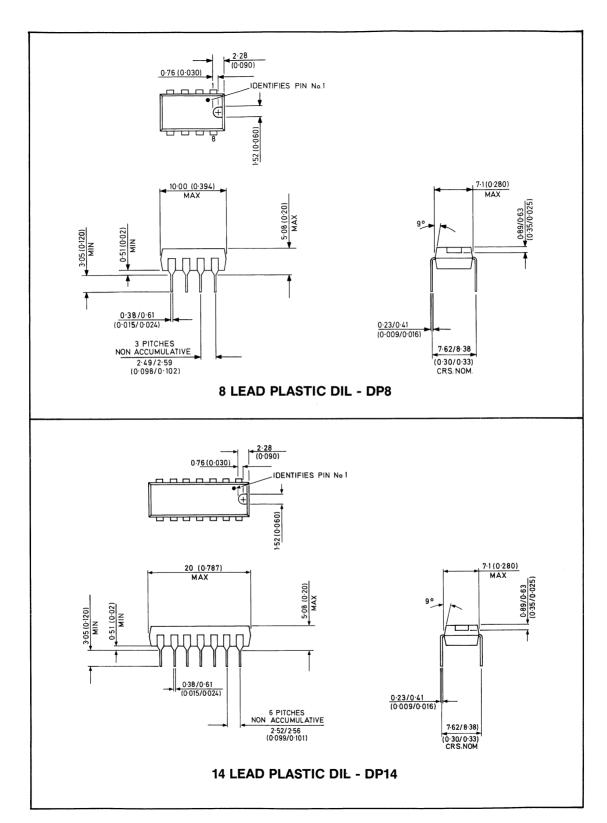

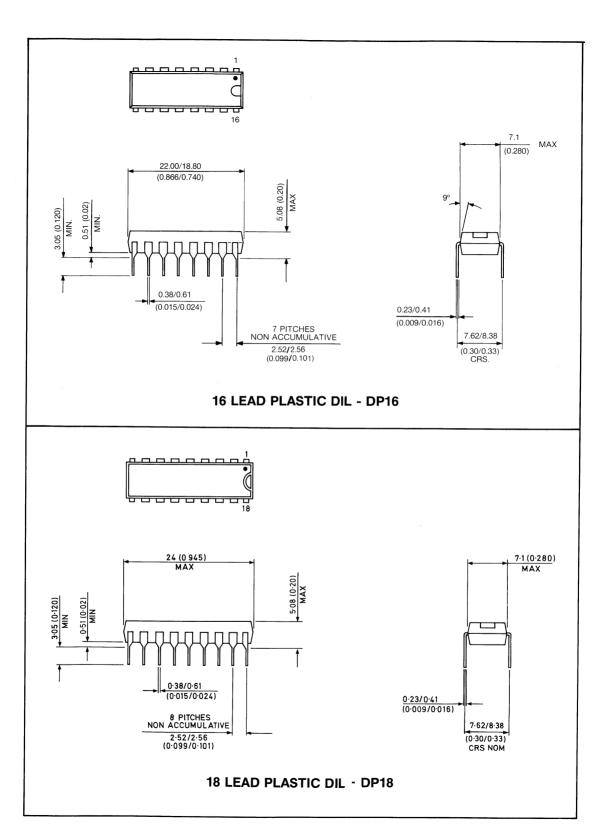

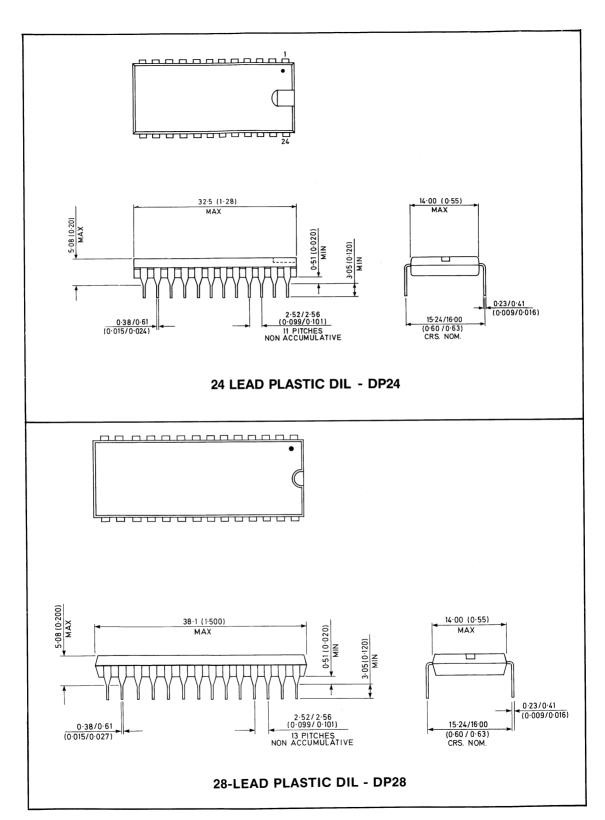

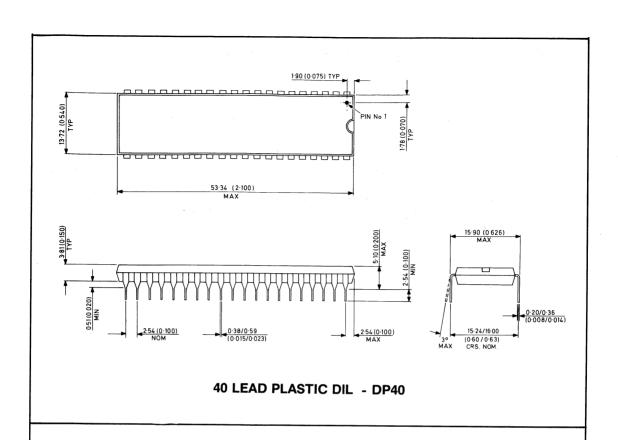

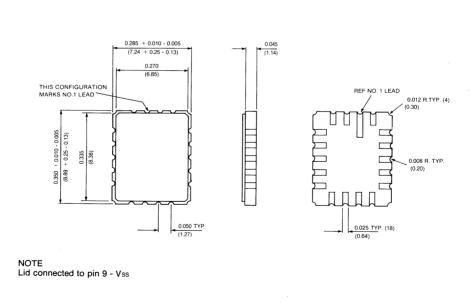

| Package outlines                    | 304  |

| Ordering information                | 312  |

| Plessey Semiconductors World-Wide   | 313  |

## Product index

| TYPE NO.                | DESCRIPTION                                                                                                                                              | PAGE       |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| CT2200                  | 32-number LED display driver, drives two 7-segment common anode LED arrays, 5-bit binary input; 1-32 display O/P, 20mA per segment; 13 direct drive O/Ps | 21         |

| ML237B                  | Negative 6-channel touch switch, with sound mute, for Neon indicators                                                                                    | 25         |

| ML238B                  | Positive 8-channel touch switch, with sound mute, for LED/Neon indicators                                                                                | 27         |

| ML239B                  | Negative 8-channel touch switch, with sound mute, for Neon indicators                                                                                    | 31         |

| ML920                   | Receiver: 20 programmes, 3 D/A, 6 other controls                                                                                                         | 33         |

| ML922                   | Receiver: 10 programmes, 3 D/A, 3 other controls                                                                                                         | 37         |

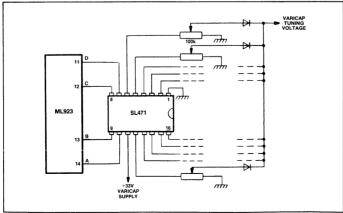

| ML923                   | Receiver: 16 channel selection codes with single analog O/P                                                                                              | 41         |

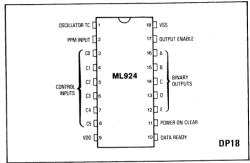

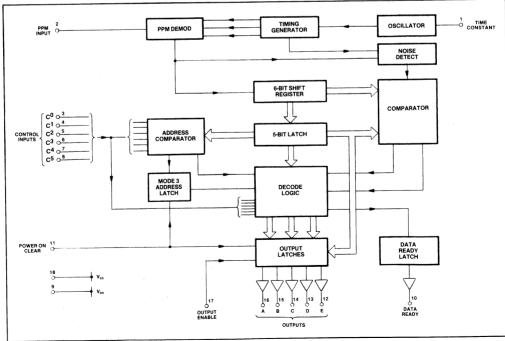

| ML924                   | Receiver: 5 digital O/Ps programmed by six control lines                                                                                                 |            |

|                         | Three selectable output modes                                                                                                                            | 45         |

| ML926                   | Receiver: 4-bit binary, 16 code momentary O/P                                                                                                            | 53         |

| ML927                   | Receiver: As ML926 but operates from second set of 16 codes                                                                                              | 53         |

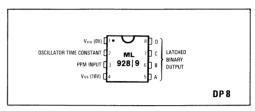

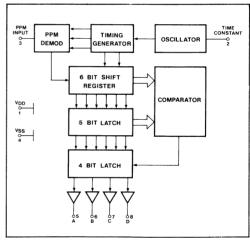

| ML928                   | Receiver: 4-bit binary 16 code latched O/P                                                                                                               | 55         |

| ML929                   | Receiver: As ML928 but operates from second set of 16 codes                                                                                              | 55         |

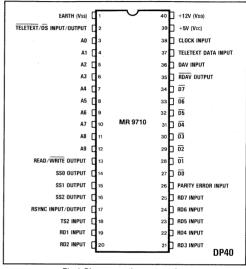

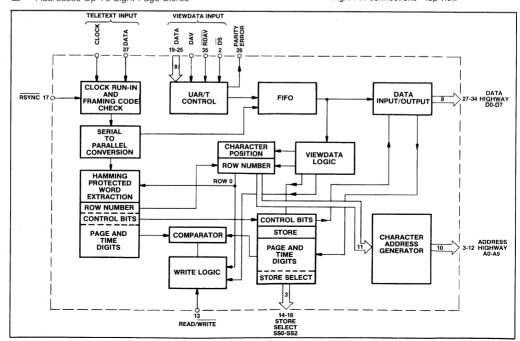

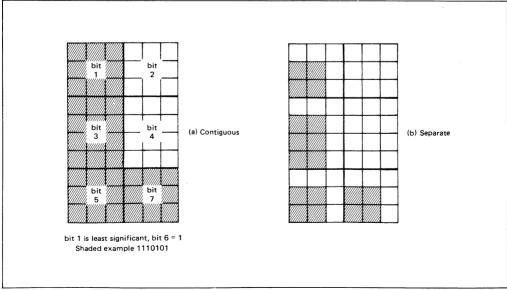

| MR9710                  | Data acquisition                                                                                                                                         | 59         |

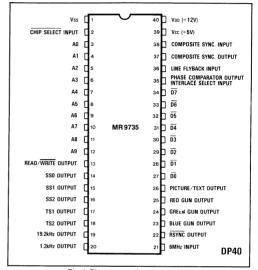

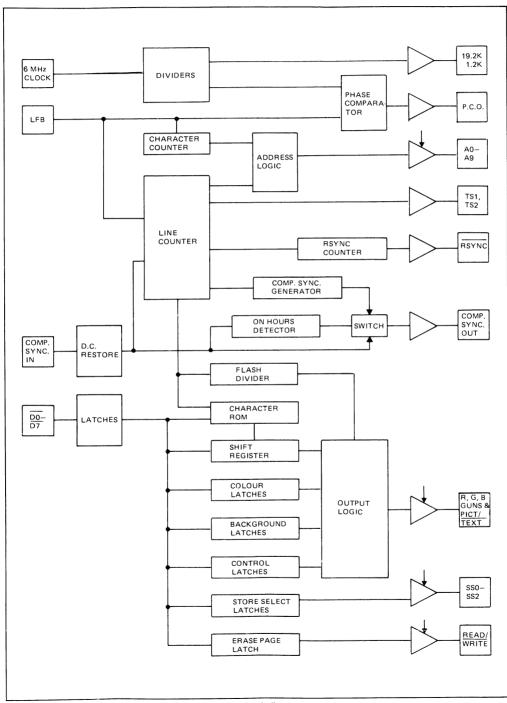

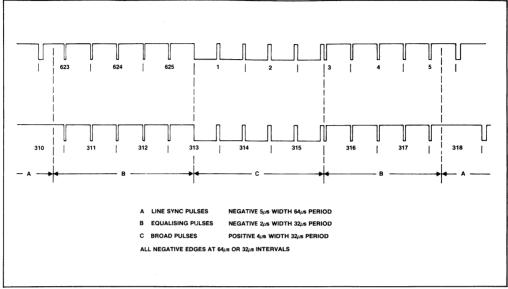

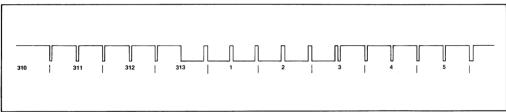

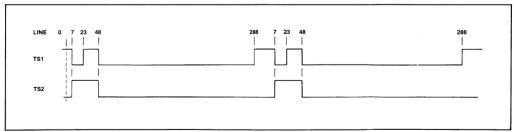

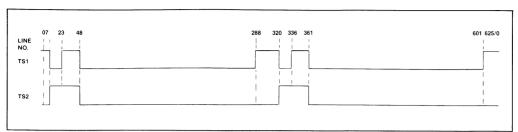

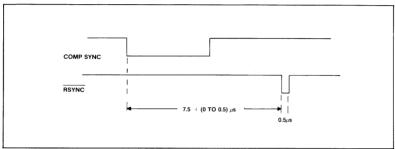

| MR9735                  | Video generator, 625 lines, interlaced/non-interlaced                                                                                                    | 67         |

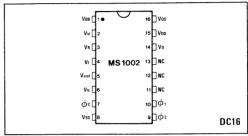

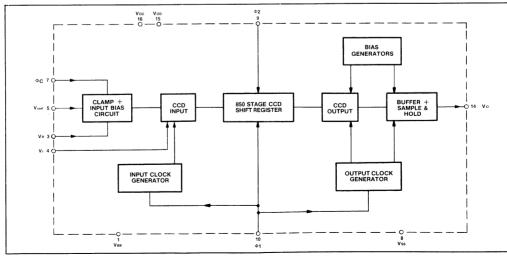

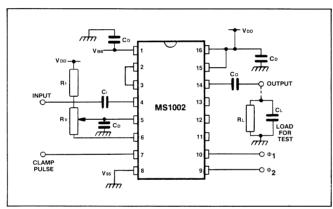

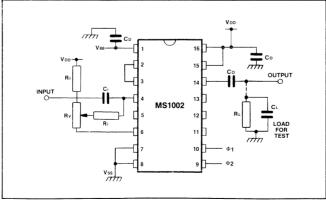

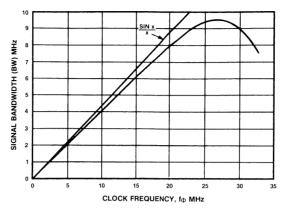

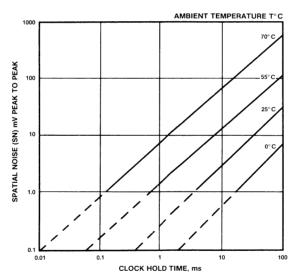

| MS1002                  | 851-bit CCD analog line store                                                                                                                            | 81         |

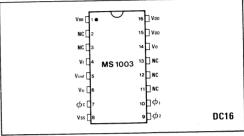

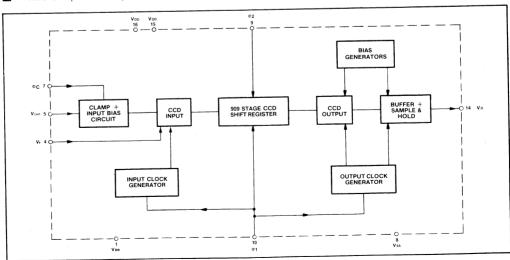

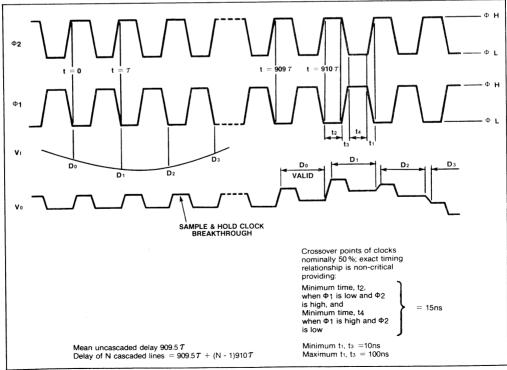

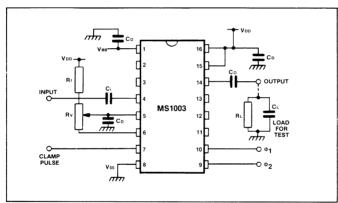

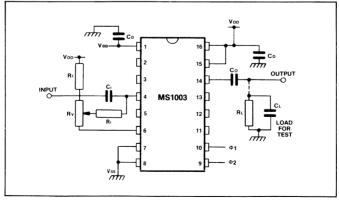

| MS1003                  | 910-bit CCD analog line store                                                                                                                            | 87<br>02   |

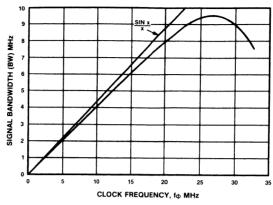

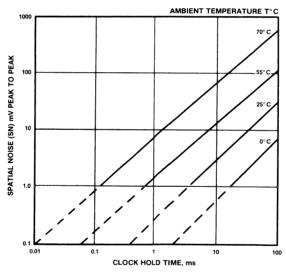

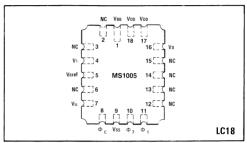

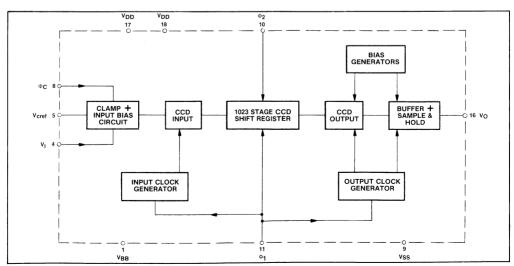

| MS1005                  | 1024-bit CCD analog line store                                                                                                                           | 93<br>269  |

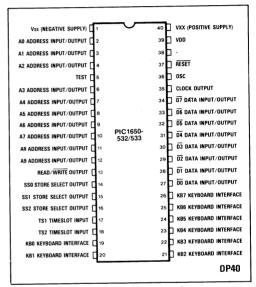

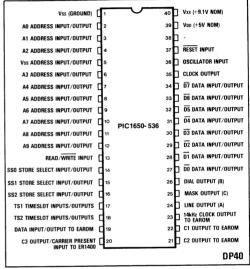

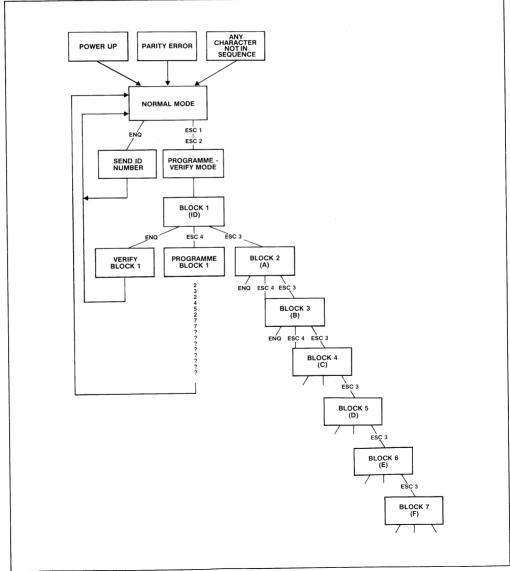

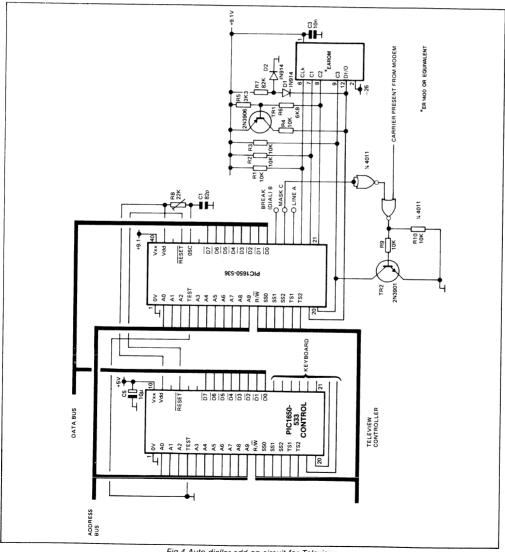

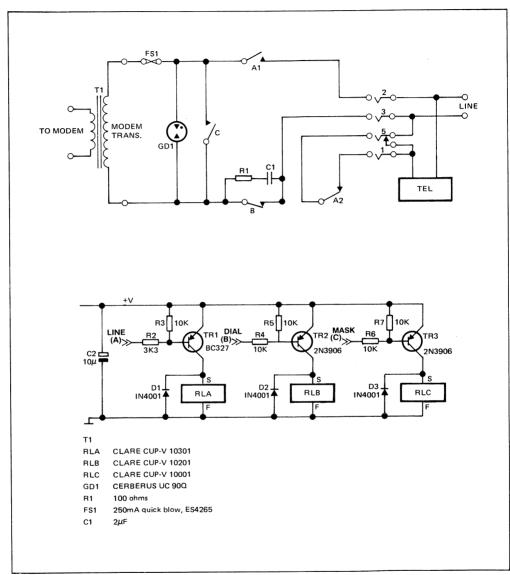

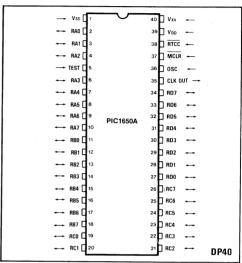

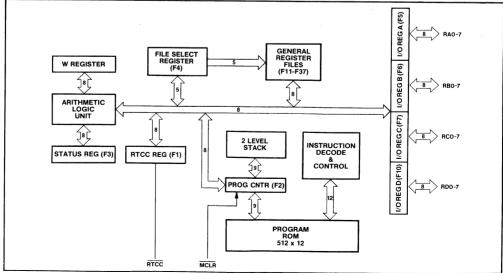

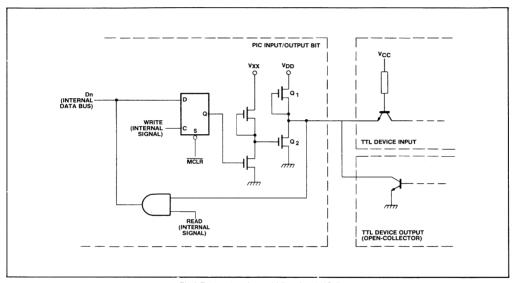

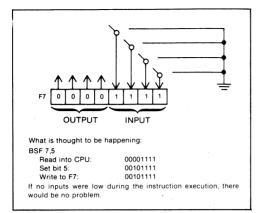

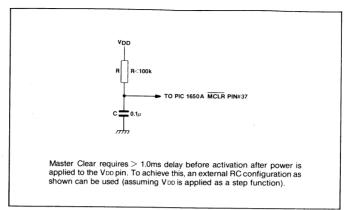

| PIC1650A<br>PIC1650-532 | 8-bit microcomputer  Alpha-numeric keyboard interface and system controller                                                                              | 209<br>99  |

| PIC1650-532             | As PIC1650-532 but Viewdata only                                                                                                                         | 99         |

| PIC1650-536             | Autodialler and terminal identifier                                                                                                                      | 113        |

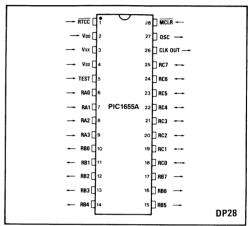

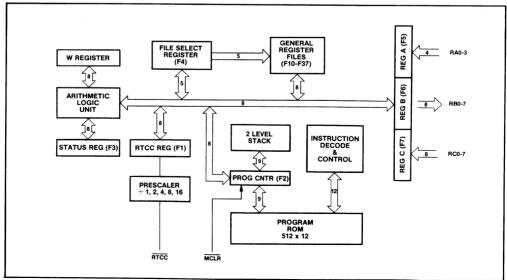

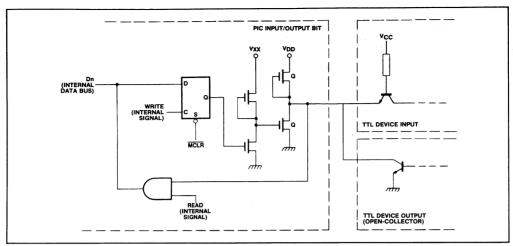

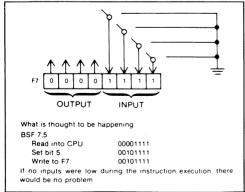

| PIC1655A                | 8-bit microcomputer                                                                                                                                      | 281        |

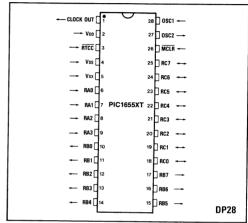

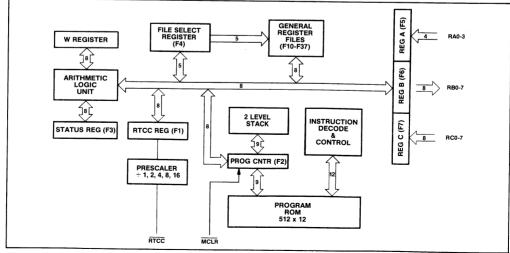

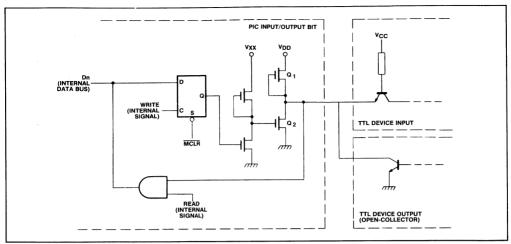

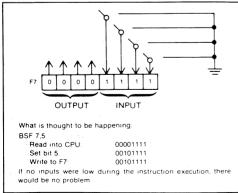

| PIC1655XT               | 8-bit microcomputer                                                                                                                                      | 293        |

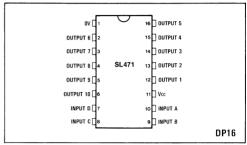

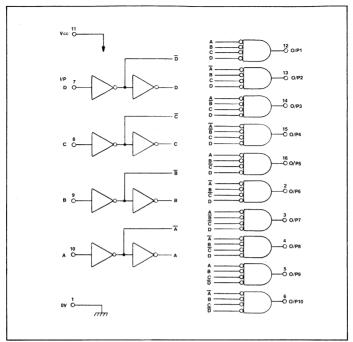

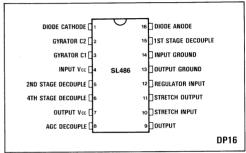

| SL471                   | BCD to 1 of 10 decoder/varicap driver                                                                                                                    | 121        |

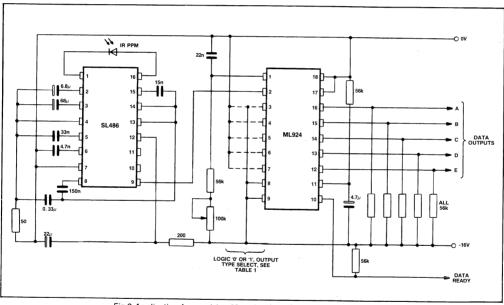

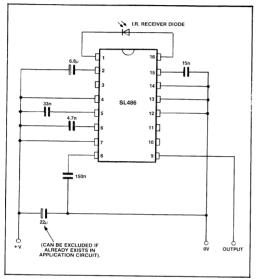

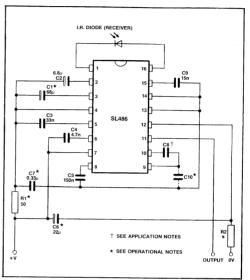

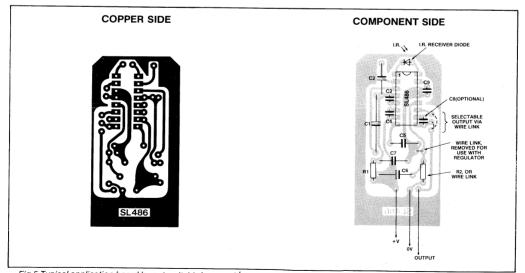

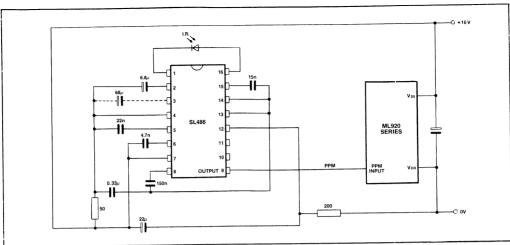

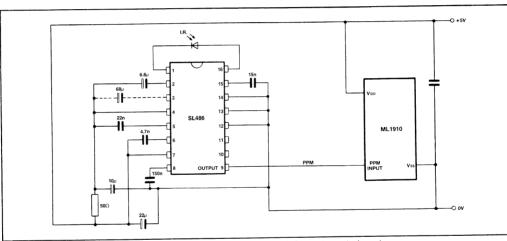

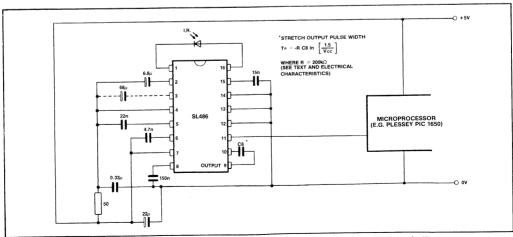

| SL486                   | Infra-red preamplifier                                                                                                                                   | 123        |

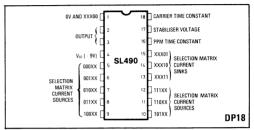

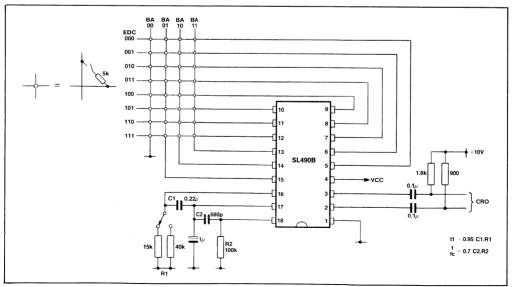

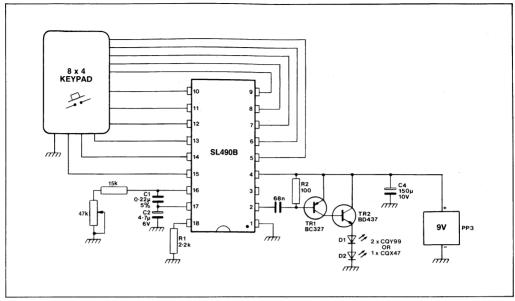

| SL490B                  | 32 code PPM transmitter, infra-red, ultrasonic or radio                                                                                                  | 129        |

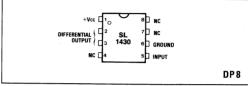

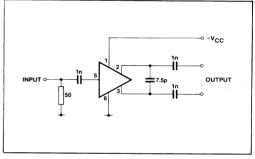

| SL1430                  | Ultra linear preamplifier, 22dB gain 100MHz, differential O/P optimised                                                                                  |            |

|                         | for driving surface acoustic wave filters                                                                                                                | 133        |

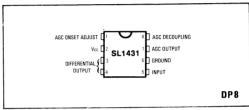

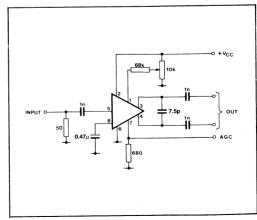

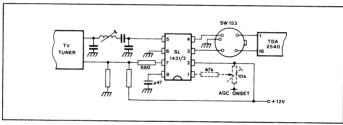

| SL1431                  | Similar to SL1430 ut with internally derived NPN tuner AGC signal O/P                                                                                    | 137        |

| SL1432                  | As SL1431 but for PNP tuners                                                                                                                             | 137        |

| SL1451                  | Wideband PLL FM detector for satellite TV                                                                                                                | 141        |

| SL1452                  | 1GHz wideband FM detector for satellite TV                                                                                                               | 143        |

| SL1454                  | Wideband linear FM detector for satellite TV                                                                                                             | 147        |

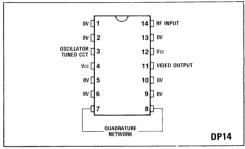

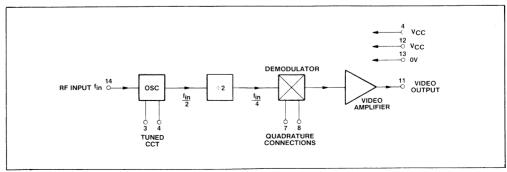

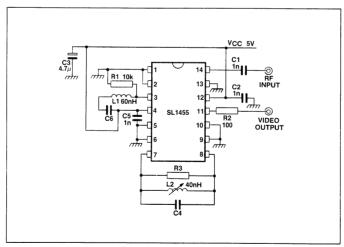

| SL1455                  | Wideband FM demodulator with threshold extension                                                                                                         | 151        |

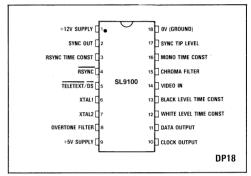

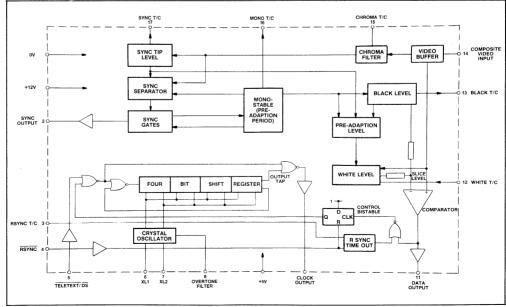

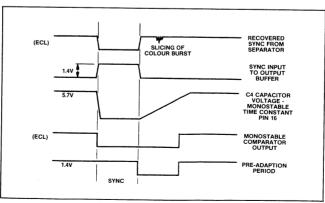

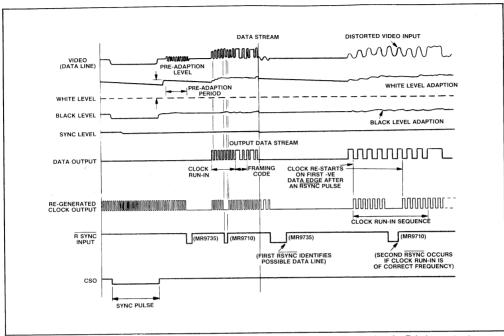

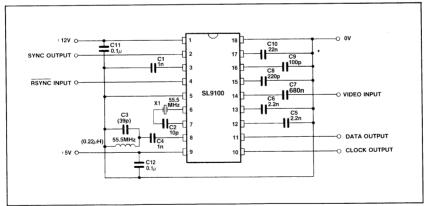

| SL9100                  | Teletext data slicer and clock regenerator                                                                                                               | 153        |

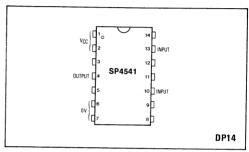

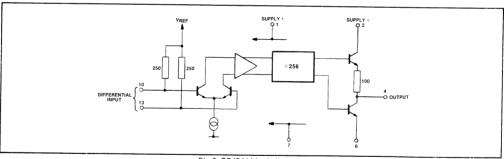

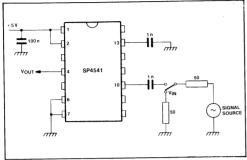

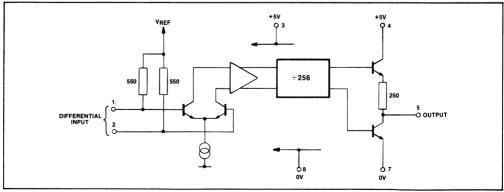

| SP4541                  | 1GHz ÷ 256, TTL O/P                                                                                                                                      | 157<br>150 |

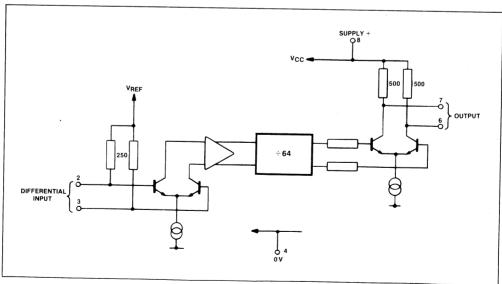

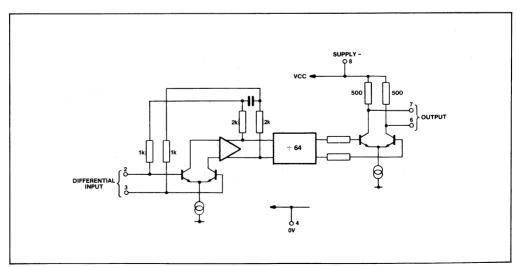

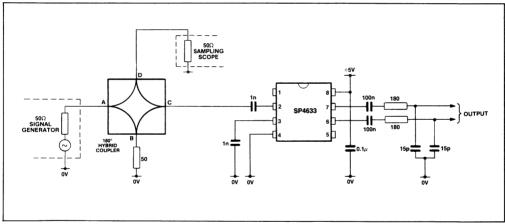

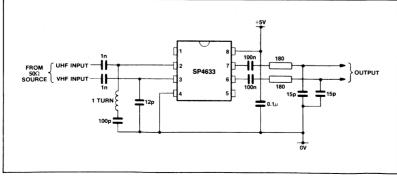

| SP4632                  | 1GHz $\div$ 64, low current, low radiation, ECL O/Ps<br>1GHz $\div$ 64 non-self oscillating, ECL O/Ps ES protected                                       | 159<br>163 |

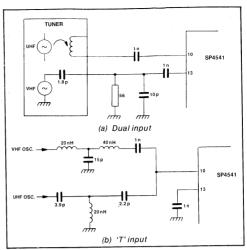

| SP4633                  | 1GHz ÷ 64, dual I/P, VHF/UHF, I/P                                                                                                                        | 163        |

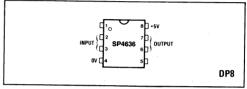

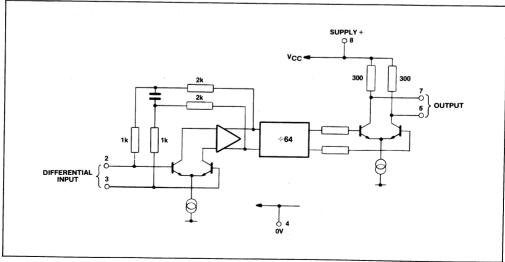

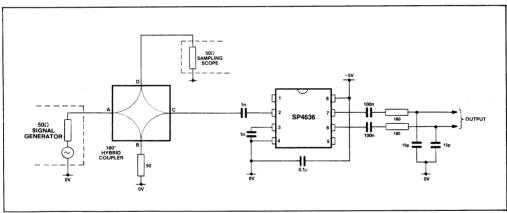

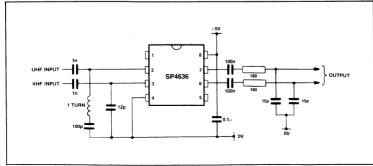

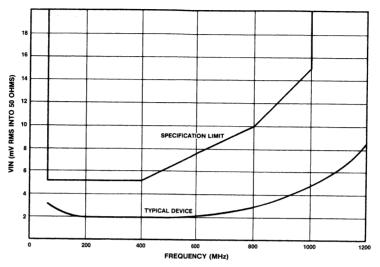

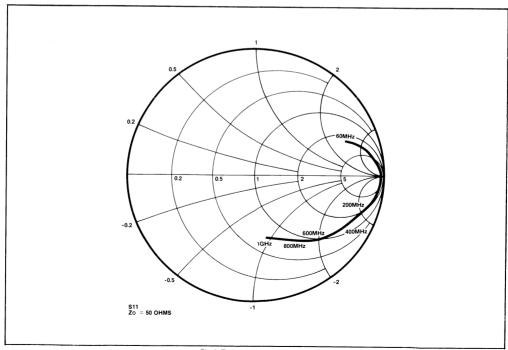

| SP4634<br>SP4636        | 1GHz ÷ 64, non-self oscillating, high O/P swing                                                                                                          | 171        |

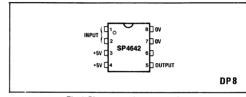

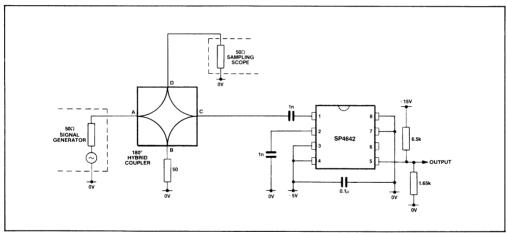

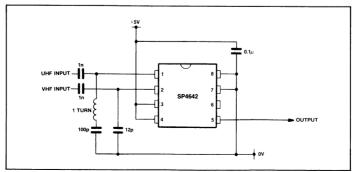

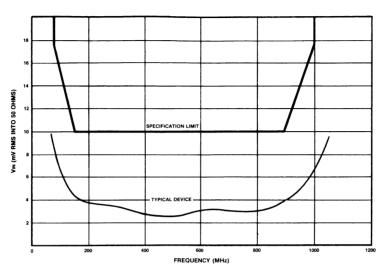

| SP4636<br>SP4642        | 1GHz ÷ 256, low current, low radiation, TTL O/P                                                                                                          | 175        |

| SP4652                  | 1GHz ÷ 256, low current, low radiation, ECL O/Ps                                                                                                         | 179        |

| SP4653                  | 1GHz ÷ 256, low current, low radiation, ECL O/Ps                                                                                                         | 183        |

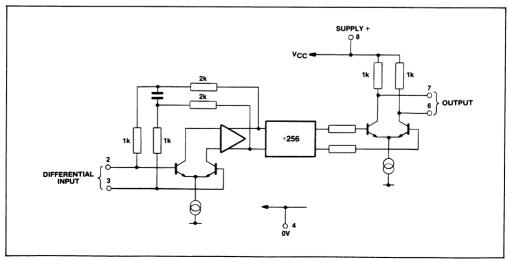

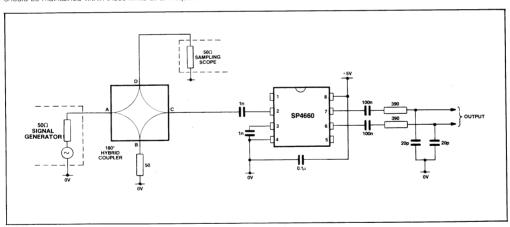

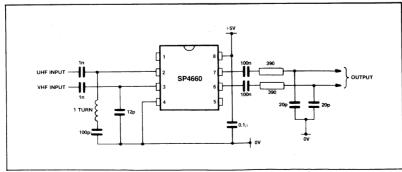

| SP4660                  | 1GHz ÷ 256, low current, low radiation, ECL O/Ps, ES protection                                                                                          | 187        |

| -                       |                                                                                                                                                          |            |

### Product index (continued)

| TYPE NO. | DESCRIPTION                                                     | PAGE |

|----------|-----------------------------------------------------------------|------|

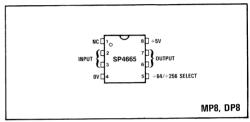

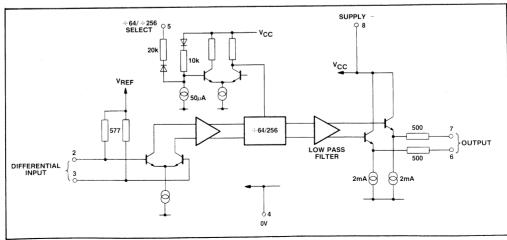

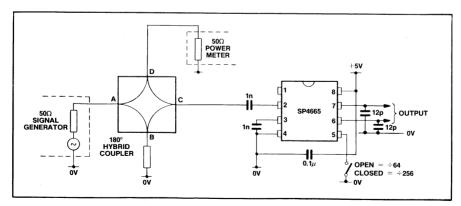

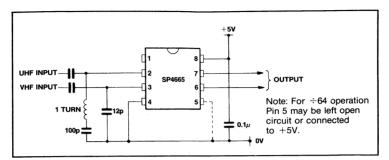

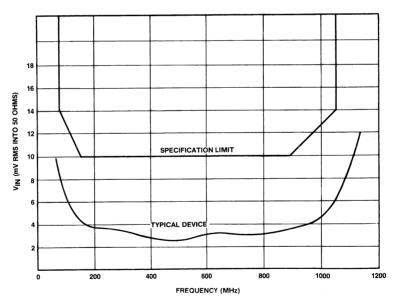

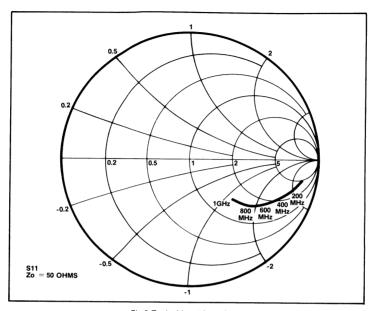

| SP4665   | 1GHz ÷ 64/256, low current, low radiation                       | 191  |

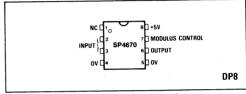

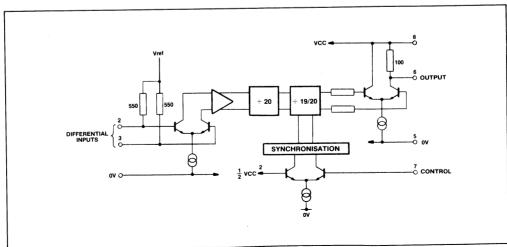

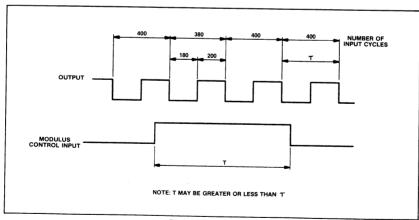

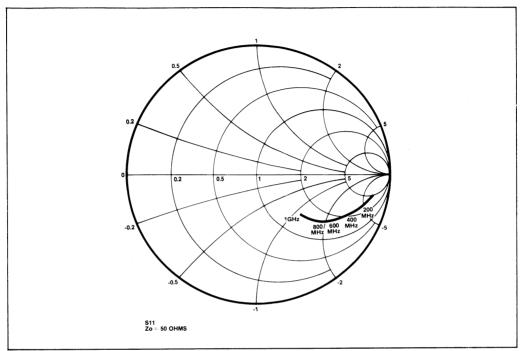

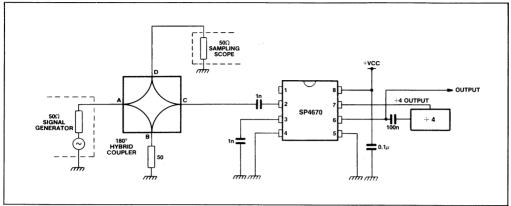

| SP4670   | 1GHz ÷ 380/400 dual modulus, single ECL O/P, latched I/P        | 195  |

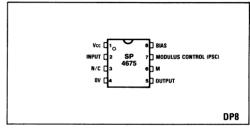

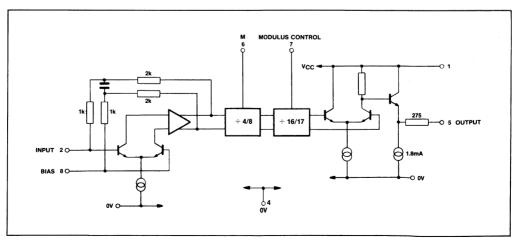

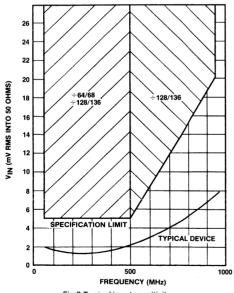

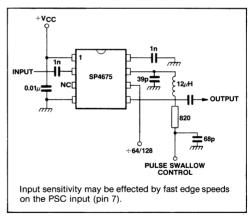

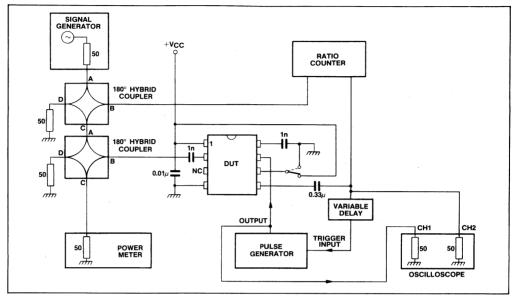

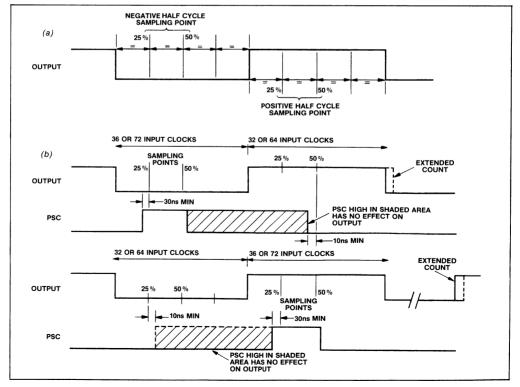

| SP4675   | 950MHz ÷ 128/136, ÷ 64/68 dual modulus prescaler                | 199  |

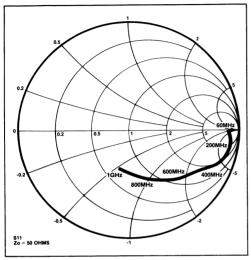

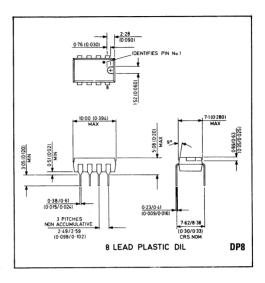

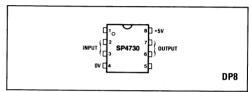

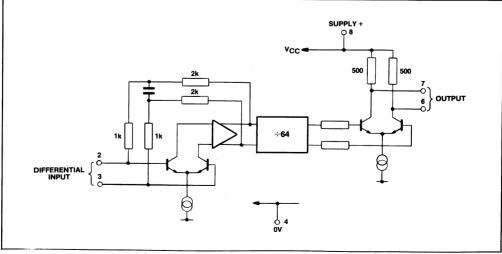

| SP4730   | 1.3GHz ÷ 64, low current, low radiation, ECL O/Ps ES protection | 203  |

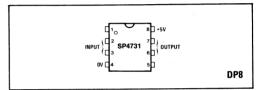

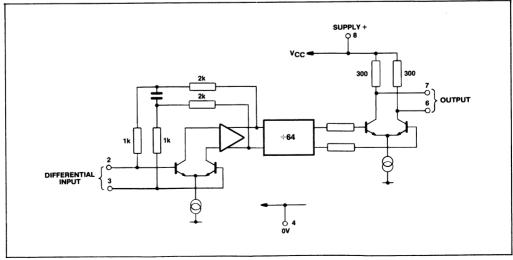

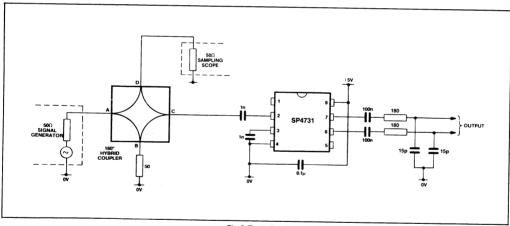

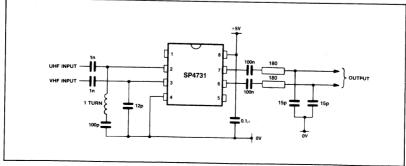

| SP4731   | 1.3GHz ÷ 64 low current, high O/P swing, ECL O/Ps               | 207  |

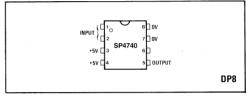

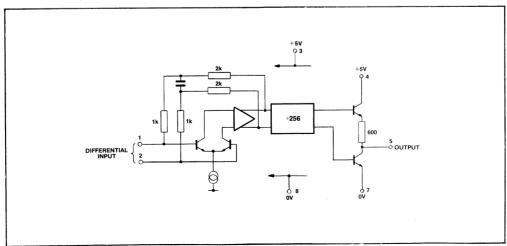

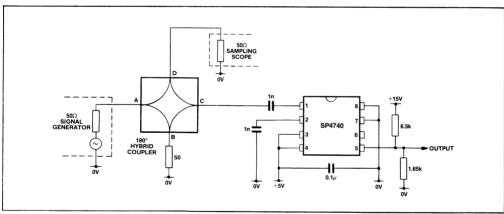

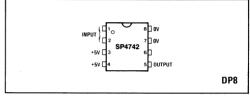

| SP4740   | 1.3GHz ÷ 256, low current, low radiation                        | 211  |

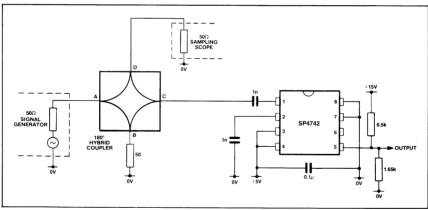

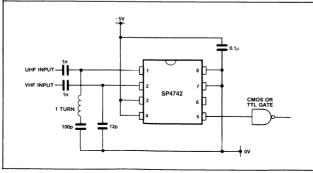

| SP4742   | 1.3GHz ÷ 256, low current, low radiation, TTL O/P               | 215  |

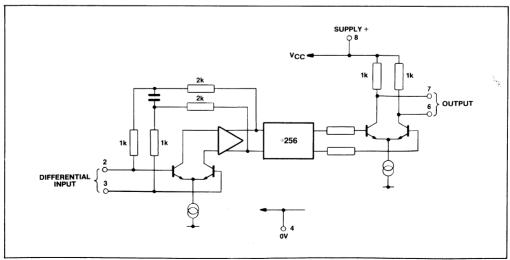

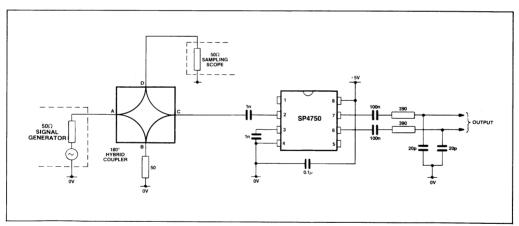

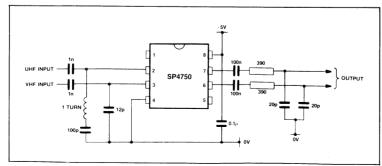

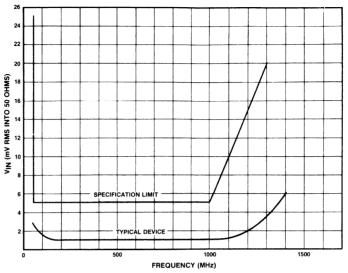

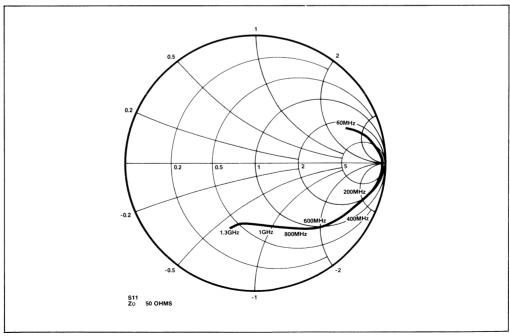

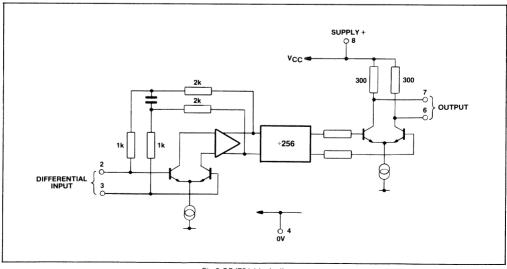

| SP4750   | 1.3GHz ÷ 256, low current, low radiation, ECL O/Ps              | 219  |

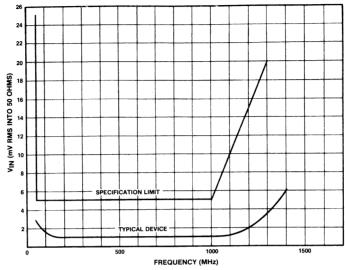

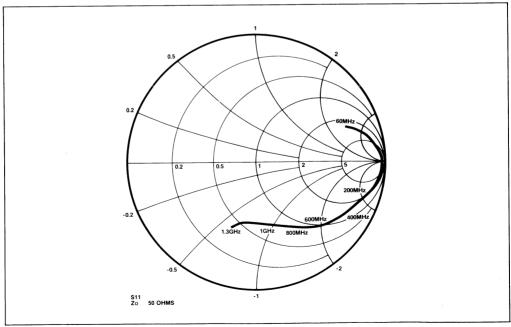

| SP4751   | 1.3GHz ÷ 256, low current, high O/P swing, ECL O/Ps             | 223  |

| SP4780   | 1.3GHz ÷ 4096/8192 dual modulus, low current, low radiation     | 227  |

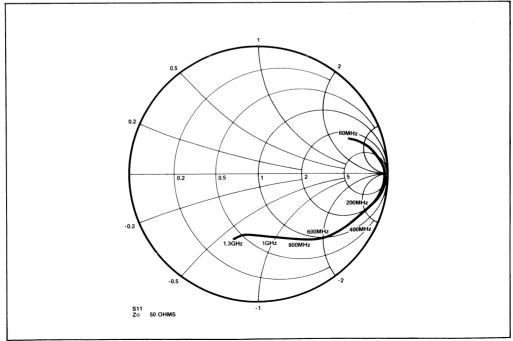

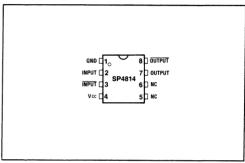

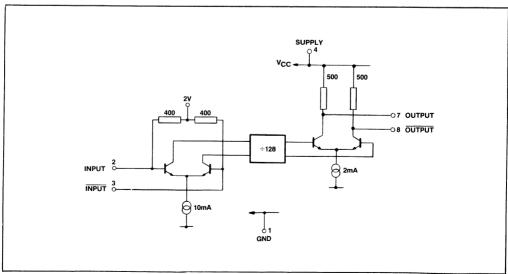

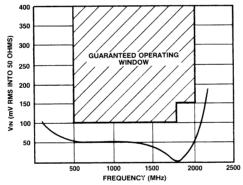

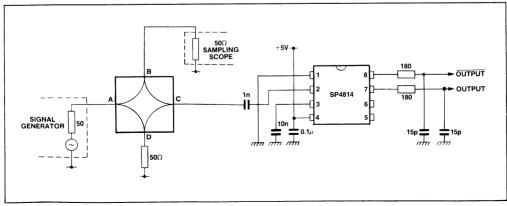

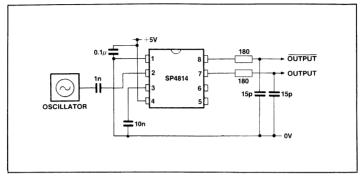

| SP4814   | 2GHz ÷ 128 prescaler                                            | 231  |

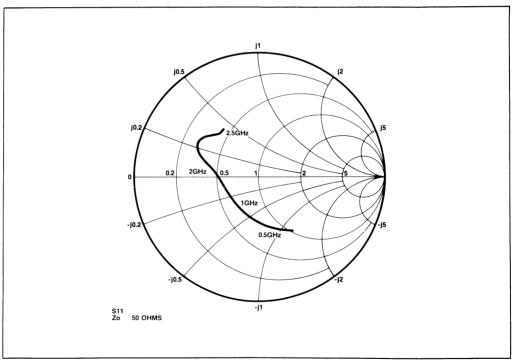

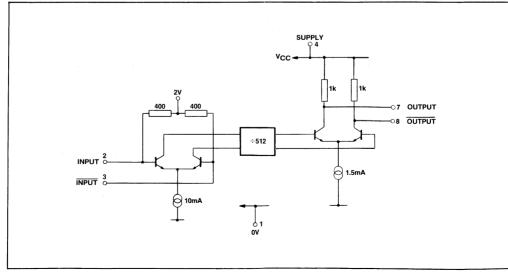

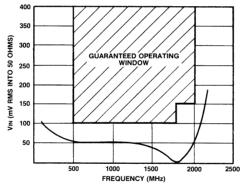

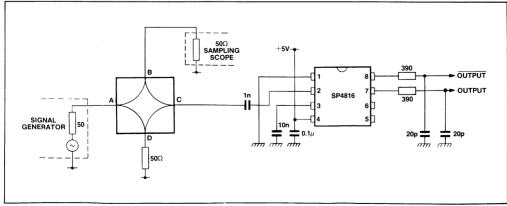

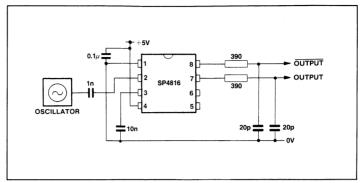

| SP4816   | 2GHz ÷ 512 prescaler                                            | 235  |

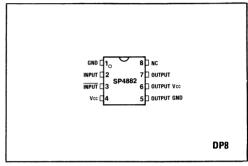

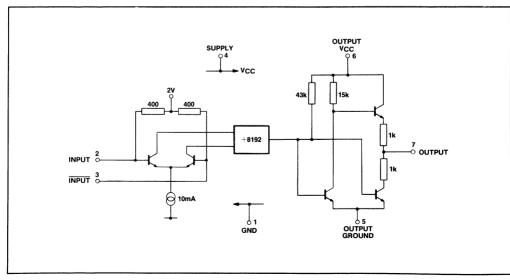

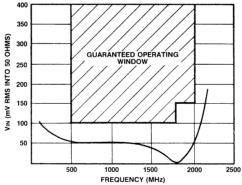

| SP4882   | 2GHz ÷ 8192 prescaler                                           | 239  |

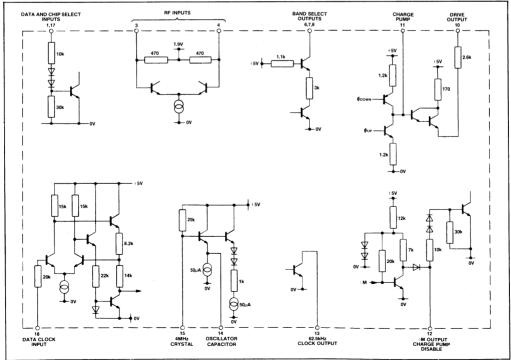

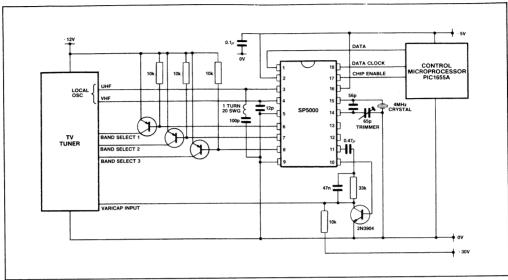

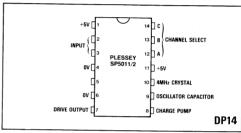

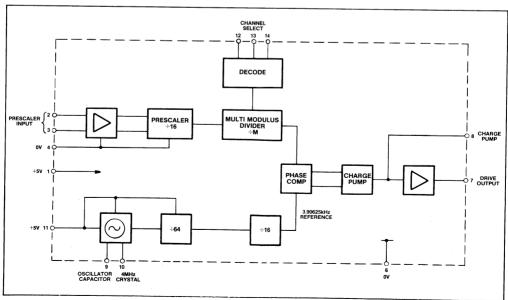

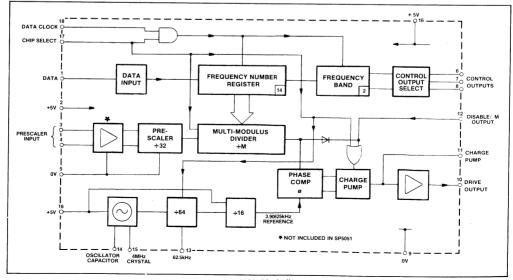

| SP5000   | Single-chip frequency synthesiser for TV tuning                 | 243  |

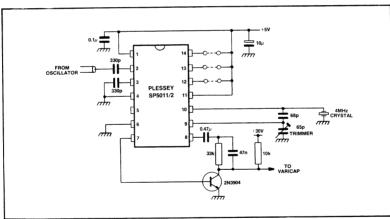

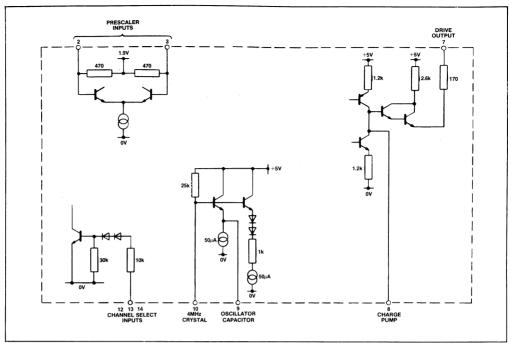

| SP5011   | 8-channel PLL up/down converter for USA                         | 249  |

| SP5012   | 8-channel PLL up/down converter for UK/Europe                   | 249  |

| SP5050   | 1.8GHz single-chip frequency synthesiser                        | 253  |

| SP5051   | 2GHz single-chip frequency synthesiser                          | 253  |

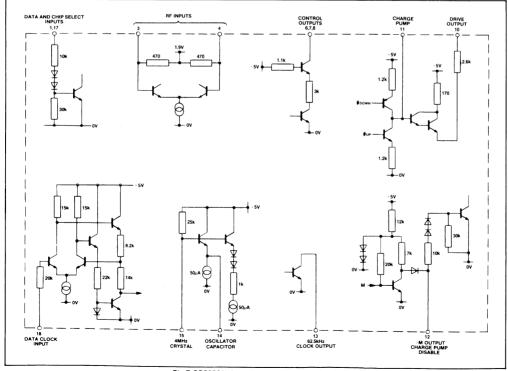

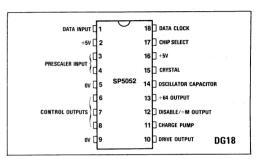

| SP5052   | 2.3GHz single-chip frequency synthesiser                        | 259  |

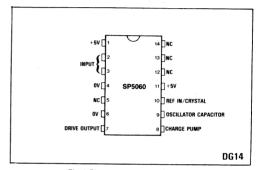

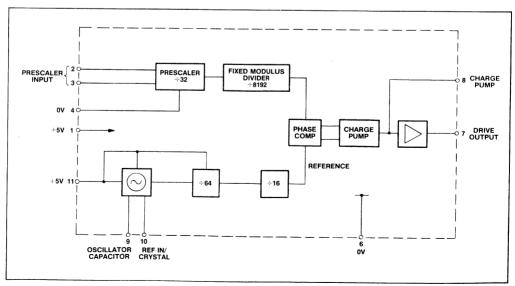

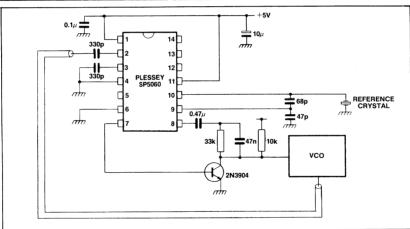

| SP5060   | 2.0GHz fixed modulus frequency synthesiser                      | 265  |

# Selection guide

| TYPE NO.         | DESCRIPTION                                                                                                         | PAGE       |

|------------------|---------------------------------------------------------------------------------------------------------------------|------------|

| Satellite F      | M detectors                                                                                                         |            |

| SL1451           | Wideband PLL FM detector for Satellite TV                                                                           | 141        |

| SL1452           | Wideband linear FM detector for Satellite TV                                                                        | 143        |

| SL1454           | Wideband linear FM detector for Satellite TV                                                                        | 147        |

| SL1455           | Wideband FM demodulator with threshold extension                                                                    | 151        |

| Tuning pr        | escalers                                                                                                            |            |

| SP4541           | 1GHz ÷ 256                                                                                                          | 157        |

| SP4632           | 1GHz ÷ 64 prescaler with low current and low radiation                                                              | 159        |

| SP4633           | 1GHz ÷ 64 non self-oscillating prescaler                                                                            | 163        |

| SP4634<br>SP4636 | 1GHz ÷ 64 dual input prescaler 1GHz ÷ 64 non self-oscillating prescaler with high output swing                      | 167<br>171 |

| SP4636<br>SP4642 | 1GHz ÷ 256 prescaler with low current and low radiation                                                             | 171        |

| SP4652           | 1GHz ÷ 256 prescaler with low current and low radiation                                                             | 179        |

| SP4653           | 1GHz ÷ 256 prescaler with low current and low radiation                                                             | 183        |

| SP4660           | 1GHz ÷ 256 prescaler with low current and low radiation                                                             | 187        |

| SP4665           | 1GHz ÷ 64/256 prescaler with low current and low radiation                                                          | 191        |

| SP4670           | 1GHz ÷ 380/400 dual modulus prescaler                                                                               | 195        |

| SP4675           | 950MHz ÷ 128/136, ÷ 64/68 dual modulus prescaler                                                                    | 199        |

| SP4730           | 1.3GHz ÷ 64 prescaler with low current and low radiation                                                            | 203        |

| SP4731           | 1.3GHz ÷ 64 high output swing low current prescaler                                                                 | 207<br>211 |

| SP4740<br>SP4742 | 1.3GHz ÷ 256 prescaler with low current and low radiation 1.3GHz ÷ 256 prescaler with low current and low radiation | 215        |

| SP4750           | 1.3GHz ÷ 256 prescaler with low current and low radiation                                                           | 219        |

| SP4751           | 1.3GHz ÷ 256 high output swing low current prescaler                                                                | 223        |

| SP4780           | 1.3GHz ÷ 4096 and ÷ 8192 prescaler                                                                                  | 227        |

| SP4814           | 2GHz ÷ 128 prescaler                                                                                                | 231        |

| SP4816           | 2GHz ÷ 512 prescaler                                                                                                | 235        |

| SP4882           | 2GHz ÷ 8192 prescaler                                                                                               | 239        |

| Tuning sy        | stems                                                                                                               |            |

| SP5000           | Single chip frequency synthesiser for TV tuning                                                                     | 243        |

| SP5011           | 8-channel PLL up/down converter for USA                                                                             | 249        |

| SP5012           | 8-channel PLL up/down converter for UK/Europe                                                                       | 249        |

| SP5050           | 1.8GHz single chip frequency synthesiser                                                                            | 253        |

| SP5051<br>SP5052 | 2GHz single chip frequency synthesiser  2.3Ghz single chip frequency synthesiser                                    | 253<br>259 |

| SP5052<br>SP5060 | 2.0GHz fixed modulus frequency synthesiser                                                                          | 265        |

| Television       |                                                                                                                     | 200        |

|                  |                                                                                                                     | 100        |

| SL1430           | TV IF preamplifier for driving SAW filters TV IF preamplifier as SL1430 with NPN tuner AGC generator                | 133<br>137 |

| SL1431<br>SL1432 | As SL1431 but for PNP tuners                                                                                        | 137        |

|                  |                                                                                                                     | .57        |

| _                | nal processing                                                                                                      | 04         |

| MS1002<br>MS1003 | 851-bit CCD analog line store 910-bit CCD analog line store                                                         | 81<br>87   |

| MS1005           | 1024-bit CCD analog line store                                                                                      | 93         |

|                  |                                                                                                                     | 30         |

## Selection guide (continued)

| TYPE NO.         | DESCRIPTION                                                               | PAGE |

|------------------|---------------------------------------------------------------------------|------|

| Remote c         | ontrol                                                                    |      |

| SL471            | BCD to 1 of 10 decoder/varicap driver                                     | 121  |

| SL486            | Infra-red preamplifier                                                    | 123  |

| SL490B           | 32 code PPM transmitter, infra-red, ultrasonic or radio                   | 129  |

| ML920            | Receiver: 20 programmes, 3 D/A, 6 other controls                          | 33   |

| ML922            | Receiver: 10 programmes, 3 D/A, 3 other controls                          | 37   |

| ML923            | Receiver: 16 channel selection codes with single analog O/P               | 41   |

| ML924            | Receiver: 5 digital O/Ps programmed by six control lines                  |      |

|                  | Three selectable output modes                                             | 45   |

| ML926            | Receiver: 4-bit binary, 16 code momentary O/P                             | 53   |

| ML927            | Receiver: As ML296 but operates from second set of 16 codes               | 53   |

| ML928            | Receiver: 4-bit binary 16 code latched O/P                                | 55   |

| ML929            | Receiver: As ML928 but operates from second set of 16 codes               | 55   |

| Display          |                                                                           |      |

| CT2200           | 32-number LED display driver, drives two 7-segment common anode           |      |

|                  | LED arrays, 5-bit binary input; 1-32 display O/P, 20mA per segment;       |      |

|                  | 13 direct drive O/Ps                                                      | 21   |

| Touch sel        | action                                                                    | 21   |

|                  |                                                                           |      |

| ML237B<br>ML238B | Negative 6-channel touch switch, with sound mute, for Neon indicators     | 25   |

| ML239B           | Positive 8-channel touch switch, with sound mute, for LED/Neon indicators | 27   |

|                  | Negative 8-channel touch switch, with sound mute, for Neon indicators     | 31   |

| Teletext         |                                                                           |      |

| MR9710           | Data acquisition                                                          | 59   |

| MR9735           | Video generator, 625 lines, interlaced/non-interlaced                     | 67   |

| PIC1650A         | 8-bit microcomputer                                                       | 269  |

| PIC1650-532      | Alpha-numeric keyboard interface and system controller                    | 99   |

| PIC1650-533      | As PIC1650-532 but Viewdata only                                          | 99   |

| PIC1650-536      | Autodialler and terminal identifier                                       | 113  |

| PIC1655A         | 8-bit microcomputer                                                       | 281  |

| PIC1655XT        | 8-bit microcomputer                                                       | 293  |

| SL9100           | Teletext data slicer and clock regenerator                                | 153  |

## The quality concept

In common with most semiconductor manufacturers, Plessey Semiconductors perform incoming piece parts check, in-line inspections and final electrical tests. However, quality cannot be inspected into a product; it is only by careful design and evaluation of materials, parts and processes - followed by strict control and ongoing assessment to ensure that design requirements are still being met - that quality products will be produced.

In line with this philosophy, all designs conform to standard layout rules (evolved with performance and reliability in mind), all processes are thoroughly evaluated before introduction and all new piece part designs and suppliers are investigated before authorisation for production use.

The same basic system of evaluation, appraisals and checks is used on all products up to and including device packing for shipment. It is only at this stage that extra operations are performed for certain customers in terms of lot qualification or release procedure.

By working to common procedures for materials and processes for all types of customers advantages accrue to all users - the high reliability user gains the advantage of scale hence improving the confidence factor in the quality achieved whilst the large scale user gains the benefits associated with basic high reliability design concepts.

Plessey Semiconductors have the following factory approvals. **BS9300** and **BS9400** (BSI Approval No. 1053/M).

**DEF-STAN 05-21** (Reg. No. 23H POD).

In addition a number of U.S., European and British customers manufacturing electronics for space have approved our facilities.

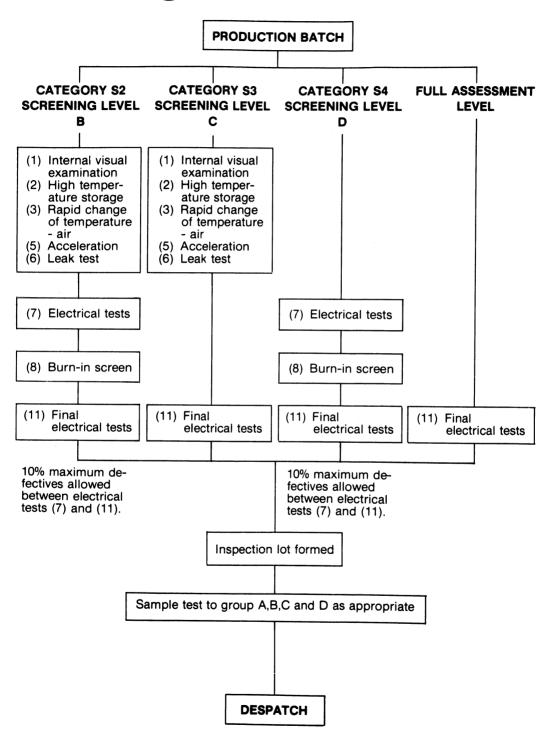

## Screening to BS9400

## Plessey Hi-Rel screening

The following Screening Procedures are available from Plessey Semiconductors.

<sup>\*</sup> Plessey Semiconductors reserve the right to change the Screening Procedure for Standard Products.

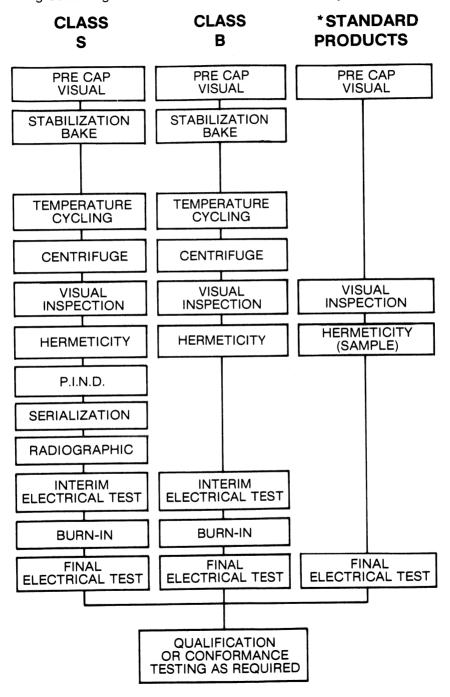

## Semi-custom design

Plessey Semiconductors' advanced work in the Semi-Custom field enables us to offer our customers the opportunity to develop their own high performance circuits using our CLASSIC software. Among the many advantages are:

• CLASSIC is cost effective and user friendly • Prototypes in 6 weeks • Close coordination with customer throughout design and production process • State-of-the-art high performance produces • Up to 10044 gates available

### Microgate-C (Si-Gate CMOS)

#### **CLA 3000 SERIES**

- Double layer metallisation

- 4 micron channel length

- Product family: CLA31XX 840 Gates CLA33XX 1440 Gates CLA35XX 2400 Gates CLA37XX 4200 Gates

- 1.6ns typ. prop delay

- 20MHz system clock rate

- 40MHz toggle rate

- Fully auto-routed

#### **CLA 5000 SERIES**

- Double layer metallisation

- 2 micron channel length

- Product family:

CLA51XX 640 Gates

CLA52XX 1232 Gates

CLA53XX 2016 Gates

CLA54XX 3060 Gates

CLA55XX 4408 Gates

CLA56XX 5984 Gates

CLA58XX 8856 Gates

CLA59XX 10044 Gates

- 1.2ns typ. prop delay

- 40MHz system clock rate

- 100MHz toggle rate

- Fully auto-routed

## Plessey Megacell TM

Now there's a VLSI design system available that's perfect for solving your Application Specific Integrated Circuit (ASIC) problems. It's **PLESSEY MEGACELL** - a complete set of advanced computer-aided engineering and design tools coupled with an advanced CMOS process for implementing VLSI integrated circuits in the system design environment.

PLESSEY MEGACELL redefines semicustom integrated circuit design. It allows system engineers to design complex circuits with a high level of confidence of first time success in silicon - thanks to one of the best simulation facilities available in the world. This greatly reduces time to market, eliminating the many prototyping iterations that are all too common now in VLSI design.

**PLESSEY MEGACELL** is just about as close as you can get to achieving hand-crafted results short of full custom itself. System engineers can directly create their designs using the advanced layout and routing tools provided - without the aid of integrated circuit designers. So none of the system designers' application expertise is ever lost in transition, while chips of the smallest size and lowest production cost are regularly achieved.

Supporting the **PLESSEY MEGACELL** design capability is one of the most advanced CMOS processes available. It uses a 2-micron geometry capable of providing performance comparable with advanced Schottky TTL, with clock speeds to 40MHz and toggle rates of 100MHz achievable. And Plessey has established a 200,000 square foot dedicated processing facility to guarantee the manufacturing capacity required by even the most aggressive volume considerations.

**PLESSEY MEGACELL** is truly the gateway to the future - custom VLSI performance, with confidence of first time success and fast time to market. And it's going to stay that way - with Plessey's commitment to add future capabilities for high-speed ECL processes, 1 micron and submicron CMOS processes, and advanced analog capabilities.

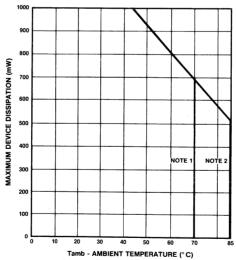

## Thermal design

The temperature of any semiconductor device has an important effect upon its long term reliability. For this reason, it is important to minimise the chip temperature; and in any case, the maximum junction temperature should not be exceeded.

Electrical power dissipated in any device is a source of heat. How quickly this heat can be dissipated is directly related to the rise in chip temperature: if the heat can only escape slowly, then the chip temperature will rise further than if the heat can escape quickly. To use an electrical analogy: energy from a constant voltage source can be drawn much faster by using a low resistance load than by using a high resistance load.

The thermal resistance to the flow of heat from the semiconductor junction to the ambient temperature air surrounding the package is made up of several elements. These are the thermal resistance of the junction-to-case, case-to-heatsink and heatsink-to-ambient interfaces. Of course, where no heatsink is used, the case-to-ambient thermal resistance is used.

These thermal resistances may be represented as

```

\begin{array}{l} \theta_{ja} = \theta_{jc} \, + \theta_{ch} \, + \theta_{ha} \\ \text{where} \, \theta_{ja} \, \text{ is thermal resistance junction-to-ambient °C/W} \\ \theta_{jc} \, \text{ is thermal resistance junction-to-case °C/W} \\ \theta_{ch} \text{ is thermal resistance case-to-heatsink °C/W} \\ \theta_{ha} \text{ is thermal resistance heatsink-to-ambient °C/W} \end{array}

```

The temperature of the junction is also dependent upon the amount of power dissipated in the device — so the greater the power, the greater the temperature.

Just as Ohm's Law is applied in an electrical circuit, a similar relationship is applicable to heatsinks.

```

T_j = T_{amb} + P_D (\theta_{ja})

T_j = \text{junction temperature}

T_{amb} = \text{ambient temperature}

P_D = \text{dissipated power}

```

From this equation, junction temperature may be calculated, as in the following examples.

#### Example 1

A device is to be used at an ambient temperature of  $+50^{\circ}$  C.  $\theta_{ja}$  for the DG14 package with a chip of approximately 1mm sq is 107° C/W. Assuming the datasheet for the device gives  $P_D = 330$ mW and  $T_1$  max  $= 175^{\circ}$  C.

```

T_j = T_{amb} + P_D \theta_{ja}

= 50 + (0.33 x 107)

= 85.31°C (typ.)

```

Where operation in a higher ambient temperature is necessary, the maximum junction temperature can easily be exceeded unless suitable measures are taken:

### Thermal design (cont'd)

#### Example 2

A device with  $T_{amb}$  max. =  $+175^{\circ}$  C is to be used at an ambient temperature of  $+150^{\circ}$  C. Again,  $\theta_{ja} = 107^{\circ}$  C/W,  $P_D = 330$ mW and  $T_j$  max. =  $+175^{\circ}$  C.

```

T_j = 150 + (0.33 \times 107)

= +185.3°C (typ.)

```

This clearly exceeds the maximum permissible junction temperature and therefore some means of decreasing the junction-to-ambient thermal resistance is required.

As stated earlier,  $\theta_{ja}$  is the sum of the individual thermal resistances; of these,  $\theta_{jc}$  is fixed by the design of device and package and so only the case-to-ambient thermal resistance,  $\theta_{ca}$ , can be reduced.

If  $\theta_{ca}$ , and therefore  $\theta_{ja}$ , is reduced by the use of a suitable heatsink, then the maximum  $T_{amb}$  can be increased:

#### Example 3

Assume that an IERC LIC14A2U dissipator and DC000080B retainer are used. This device is rated as providing a  $\theta_{ja}$  of 55° C/W for the DG14 package. Using this heatsink with the device operated as in Example 2 would result in a junction temperature given by:

$$T_j = 150 + (0.33 \times 55)$$

= 168° C

Nevertheless, it should be noted that these calculations are not necessarily exact. This is because factors such as  $\theta_{jc}$  may vary from device type to device type, and the efficacy of the heatsink may vary according to the air movement in the equipment.

In addition, the assumption has been made that chip temperature and junction temperature are the same thing. This is not strictly so, as not only can hot spots occur on the chip, but the thermal conductivity of silicon is a variable with temperature, and thus the  $\theta_{jc}$  is in fact a function of chip temperature. Nevertheless, the method outlined above is a practical method which will give adequate answers for the design of equipment.

It is possible to improve the dissipating capability of the package by the use of heat dissipating bars under the package, and various proprietary items exist for this purpose.

Under certain circumstances, forced air cooling can become necessary, and although the simple approach outlined above is useful, more factors must be taken into account.

# Plessey ICs for Satellite Reception

Plessey Semiconductors are one of the world's leading suppliers of high frequency Integrated Circuits. Our long experience in supplying high performance high quality circuits for military applications together with our experience in supplying high volume products to the cable TV and broadcast TV manufacturing industry has put us in a strong position to supply the newly emerging Satellite Reception market.

To enable manufacturers to design and produce Satellite Receiver Equipment in time for this potentially very large market, Plessey Semiconductors have brought together their expertise to produce the key ICs required.

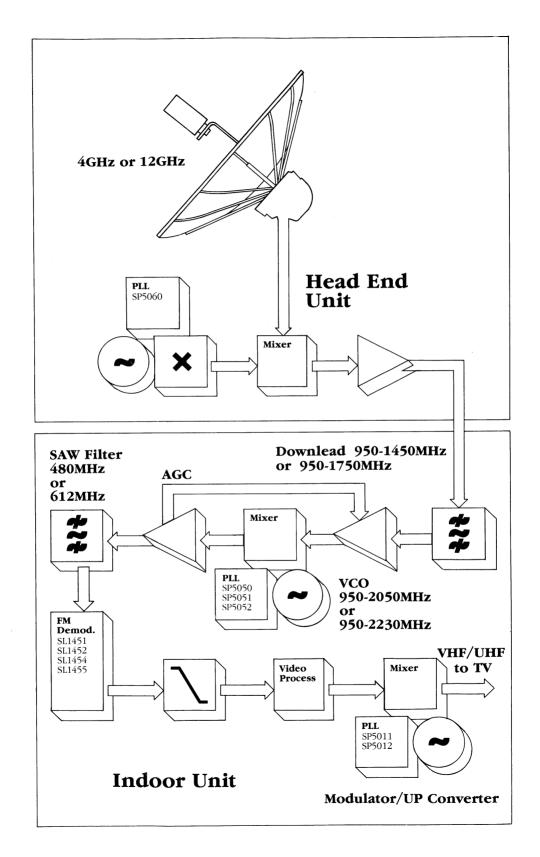

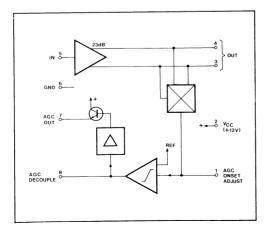

### Typical Satellite Receiver System

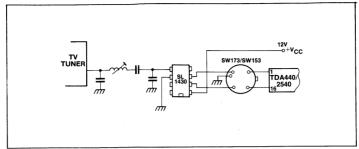

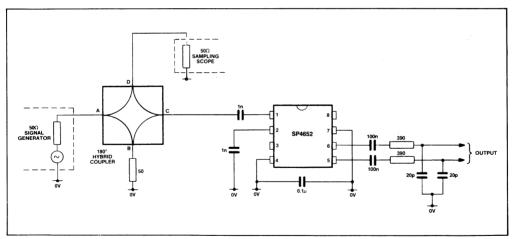

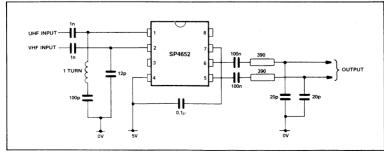

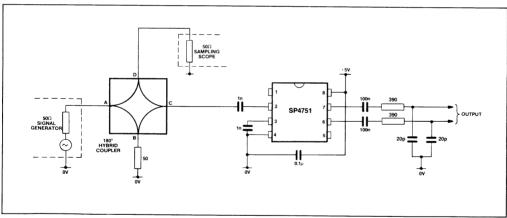

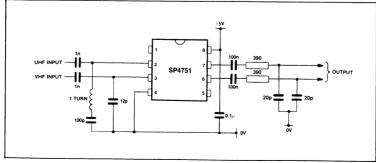

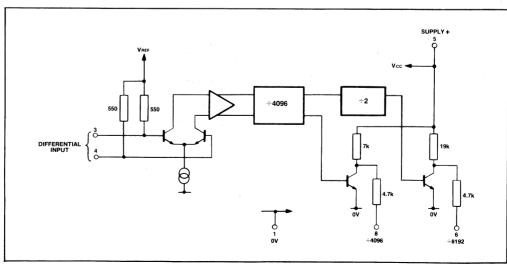

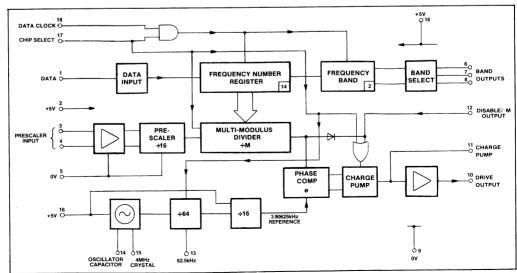

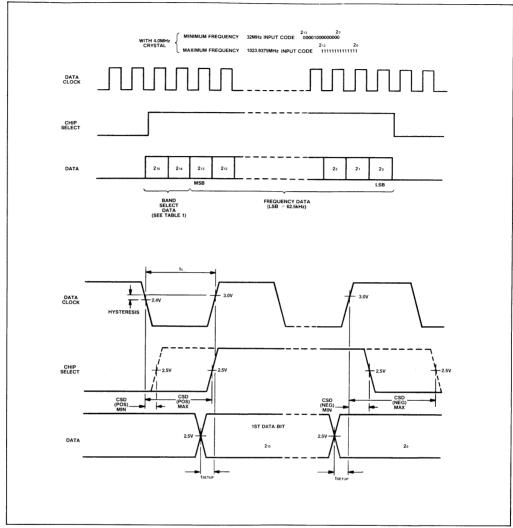

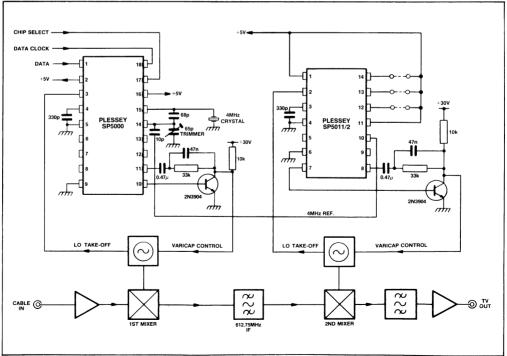

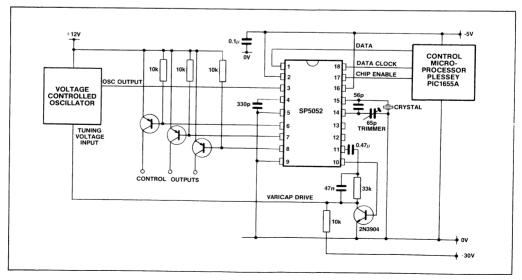

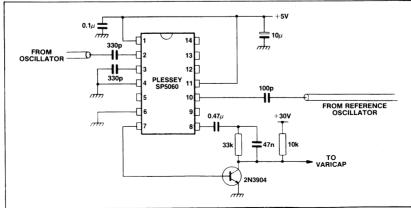

The head end (outdoor) unit mixes the incoming 4 or 12GHz signal down to one of the frequencies shown in the block diagram. This is achieved by multiplying an oscillator controlled by Plessey's SP5060 PLL. After mixing the resultant signal is buffered and sent down a coax link to the indoor unit.

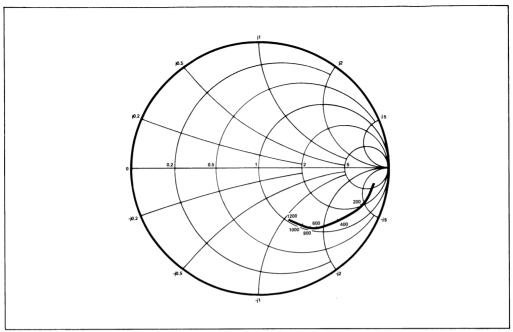

The signal is amplified at the indoor unit after passing through a wideband filter. This amplifier may incorporate AGC to provide the optimum signal level for the mixer and subsequent stages. The required signal is selected from the band by mixing with the output from a PLL controlled oscillator using Plessey's SP5051 or SP5052 and converted to a second IF of between 380MHz - 650MHz.

The high second IF greatly simplifies design problems by placing the image at a point which obviates the need for tracking filters.

After mixing, the signal passes through another amplifier to make up the losses of the following SAW filter. The AGC feedback signal is also detected at this point.

After passing through the SAW filter, which must be capable of passing the FM signal without loss of information, detection is performed by one of the range of Plessey FM demodulators. These devices can operate at frequencies well above the highest common IF of 612.75MHz with minimal signal distortion and give excellent threshold performance.

The detected signal will then be decoded and descrambled as required. Here Plessey can offer its long experience in CCD technlogy and Semi-custom design in Bipolar and CMOS technology.

Finally the signal will be converted up to a suitable channel for connection to the standard TV input using an SP5011 or SP5012 to give accurate PLL control of the frequency with a number of alternative options.

### **Technical Specification**

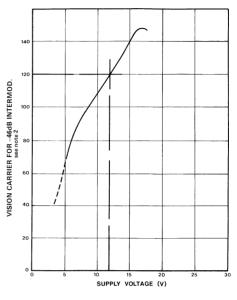

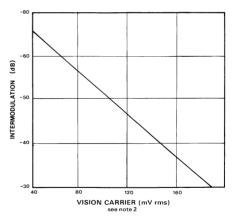

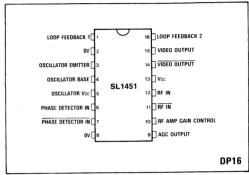

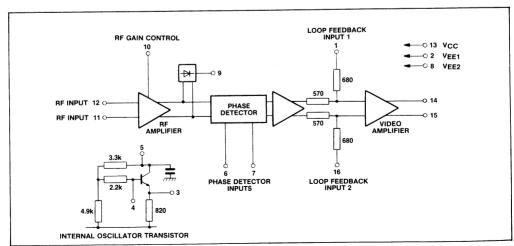

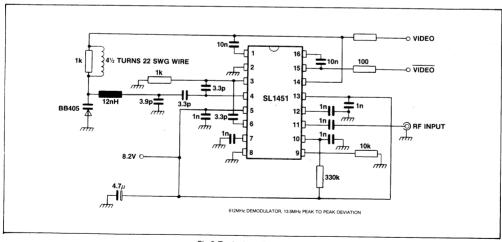

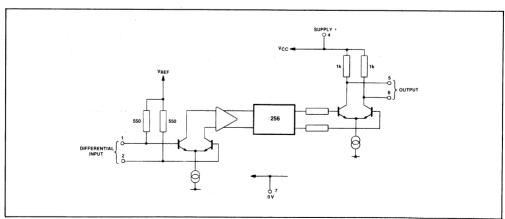

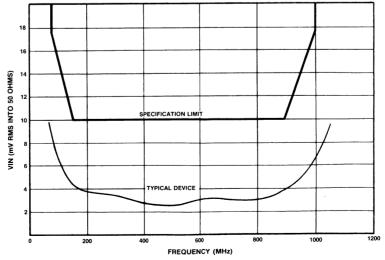

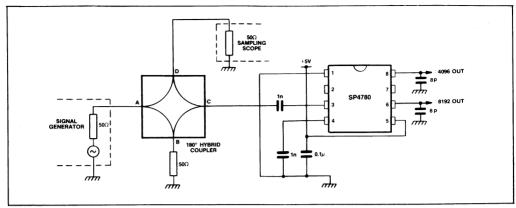

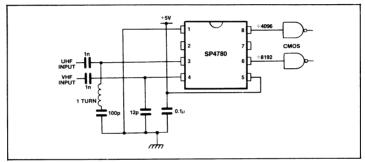

**SL1451** This is a PLL FM wideband detector, designed for satellite receivers employing an IF of 380 to 700MHz. This device gives threshold extension for improved system performance.

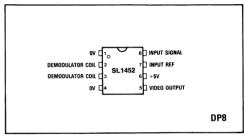

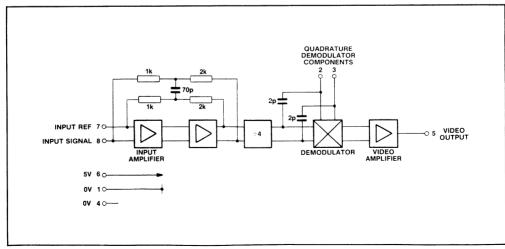

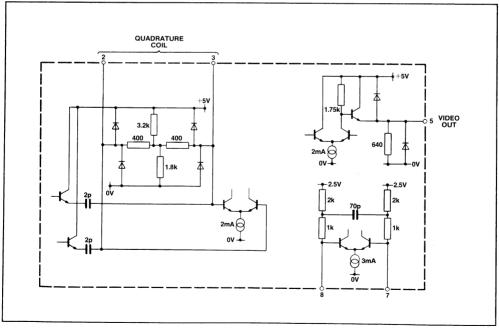

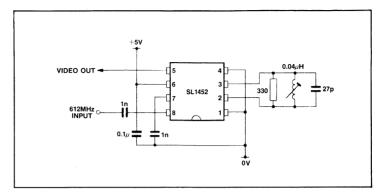

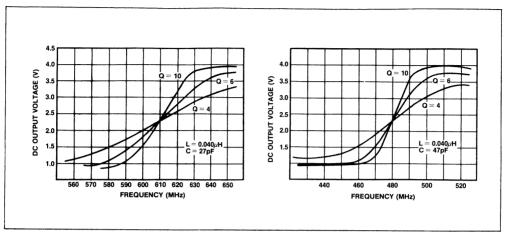

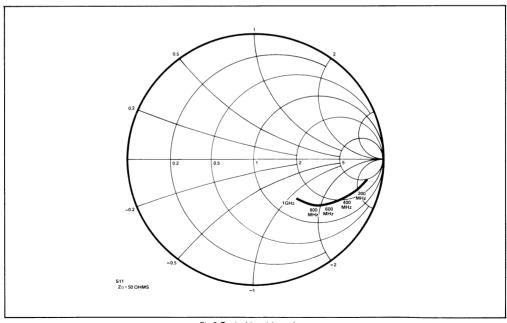

**SL1452** This is an FM wideband detector designed to operate in satellite reception systems employing high IF of between 400-1000MHz. Using a high IF eliminates the need for a tracking filter for Image rejection and so greatly simplifies system design.

The other advantage is that the deviation is a small percentage of the IF and very good linearity is achieved.

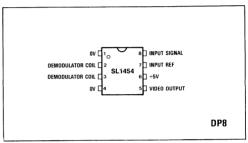

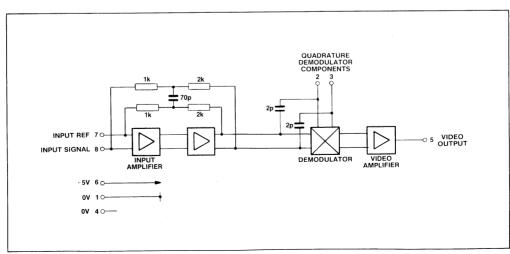

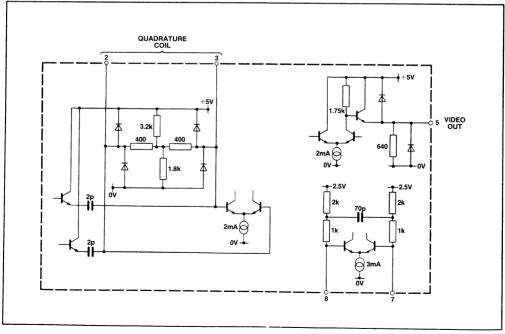

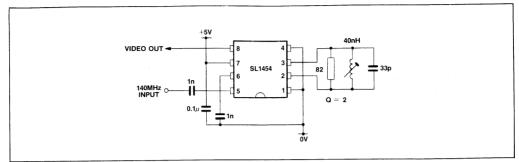

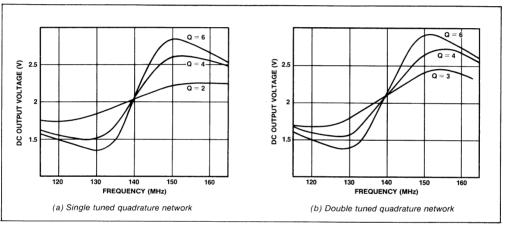

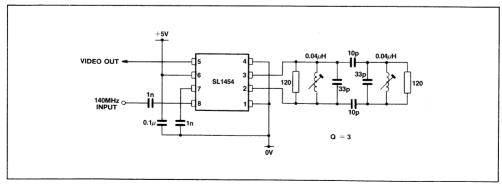

**SL1454** This is an FM wideband detector designed to operate in satellite receivers using an IF of between 70 and 150MHz.

**SL1455** This is an FM wideband detector designed to operate in satellite receivers using an IF of 300 to 700MHz. The SL1455 gives threshold extension for improved system performance.

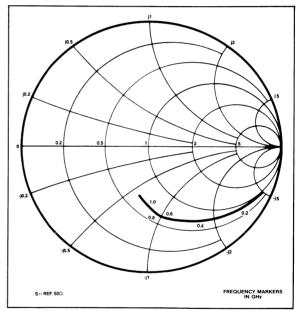

**\$L5060** This is a PLL for use in the head end unit. It needs no microprocessor but can synthesise any frequency in the range 500MHz to 2.0GHz by appropriate choice of reference frequency. This, together with a frequency doubling mixer, enables C-Band (4GHz) signals to be block-converted down to a standard first IF of 950MHz to 1450MHz.

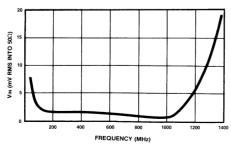

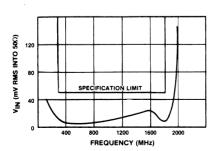

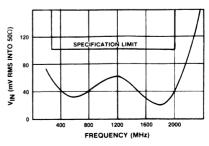

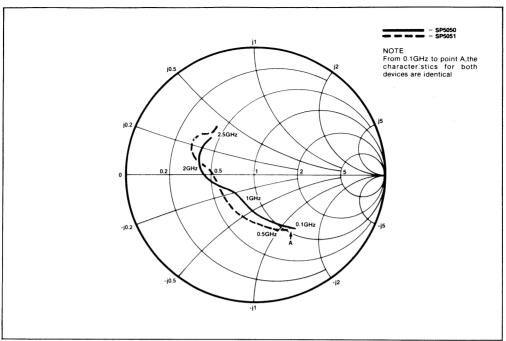

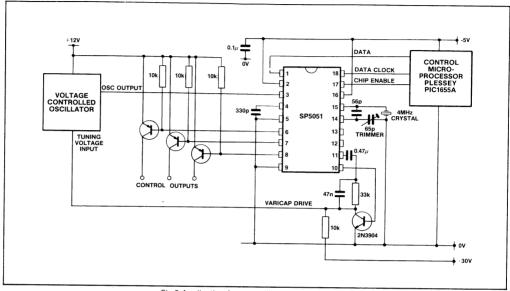

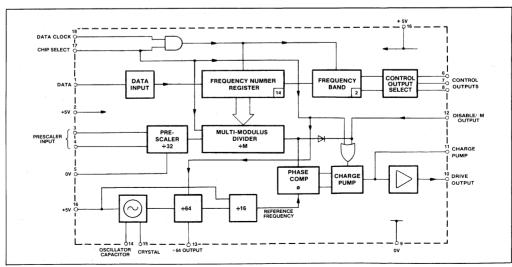

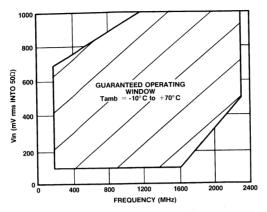

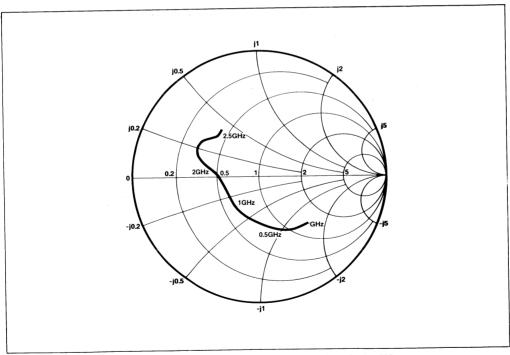

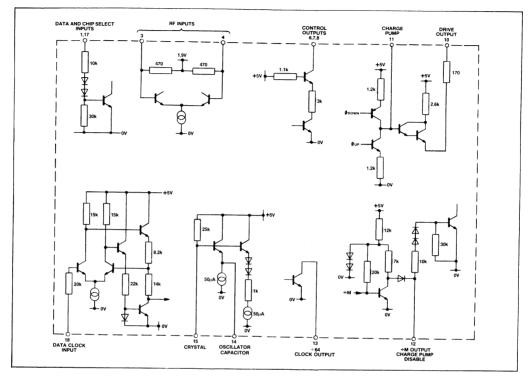

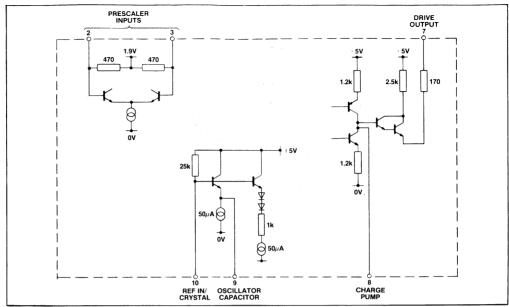

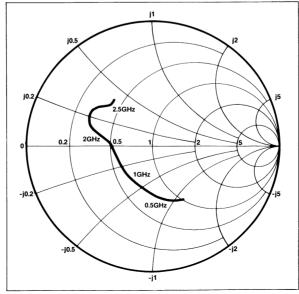

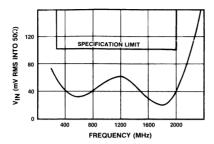

**SP5050/1/2** These are single chip PLL controllers. The SP5050 offers 50mV sensitivity at 1.8GHz, the SP5051 is a 100mV, 2.0GHz device while the SP5052 is a similar device, specified to 2.3GHz.

These devices can be used to control the local oscillator of the second mixer stage.

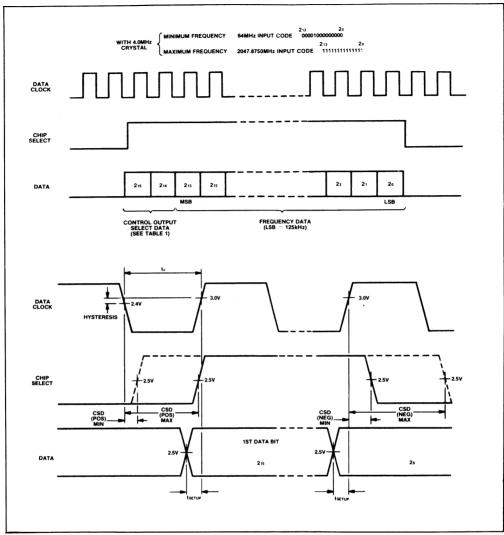

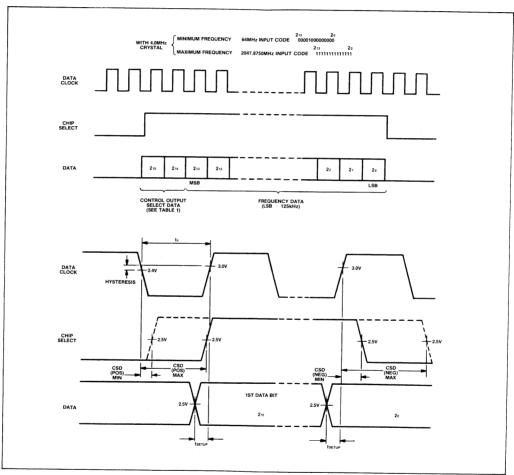

The required channel is selected at the second stage by mixing the signal down to an IF which will usually be 480MHz for European systems and 510MHz or 612.75MHz for USA/Canadian systems. The SP5050/1/2 are controlled by a 16 bit word from a 4 or 8 bit micro which gives 125kHz steps over the range.

Since the oscillator runs higher than the incoming signal, full band systems could require a PLL to operate up to 2.4GHz.

Plessey offer a  $\div 4$  SP8712 together with a standard SP5000 PLL to achieve this. Further prescaler options with high prescaler ratios are in development for this top end of the frequency requirement.

**SP5011/2** Fixed frequency versions of the original SP5000 PLL controller needing no microprocessor control. These devices give eight options of PLL controlled frequency conversion. They can be used to convert the baseband signal up to a UHF or VHF channel for connection to the TV or conversion from VHF cable frequencies up to UHF or higher VHF channels.

**Amplifiers** Plessey produce a range of high frequency amplifiers which is being further extended to 2GHz for Satellite Reception systems.

# Technical Data

#### **ADVANCE INFORMATION**

Advance information is issued to advise Customers of new additions to the Plessey Semiconductors range which, nevertheless, still have 'pre-production' status. Details given may, therefore, change without notice although we would expect this performance data to be representative of 'full production' status product in most cases. Please contact your local Plessey Semiconductors Sales Office for details of current status.

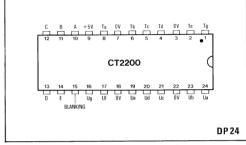

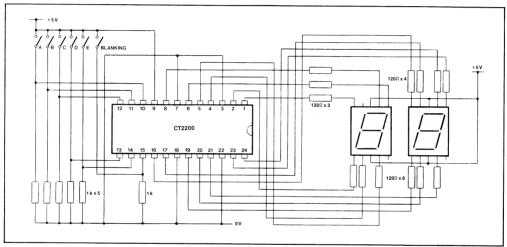

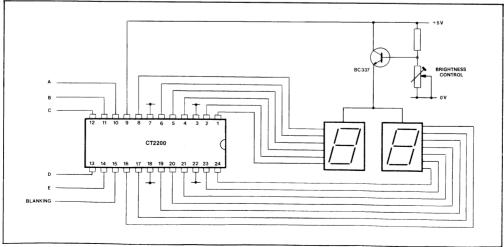

### CT2200

#### 5-BIT BINARY TO 13-SEGMENT DECODER/DRIVER

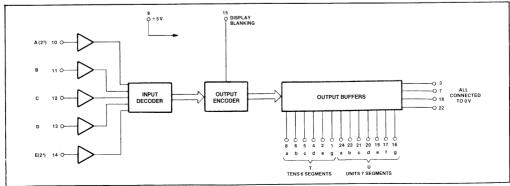

The CT2200 is an N-channel MOS integrated circuit, designed to directly drive two 7-segment LEDs to display the numbers 1 to 32, with leading zeros suppressed. The circuit is ideal for applications such as the programme number display of a television receiver. The display is controlled by a 5-bit binary input port, weighted so that the number shown (1-32) is one more than the binary input (0-31) to avoid programme 0. The 5 lines can come from a remote control receiver or from any other source of continuous 5-bit data.

Common anode LEDs can be driven directly with a current limiting resistor in series with each output (see Fig.5) or by using some other form of brightness control (see Fig.6). By driving each segment individually the interference problems associated with multiplexed displays are avoided.

A blanking input is provided so that the display can be turned off or can be made to flash with an external pulsed signal.

Only 13 lines are needed for two 7-segment displays because segment Tf is never lit for the numbers 1 to 32 and so does not need to be decoded and driven. Segment identification is shown in Fig.2.

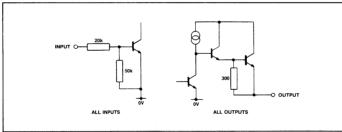

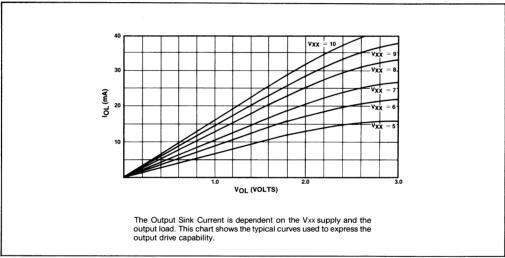

The 13 outputs of the output encoder drive the gates of large output transistors to give two states: OFF and SINK CURRENT; as there can be up to 12 outputs on at once, each sinking 20mA, four 0V pins are provided to reliably carry this current. ALL FOUR PINS (3, 7, 18, 22) MUST BE CONNECTED TO 0 V.

The number of segments required for each character is shown in Fig.3.

Fig.2 Segment identification

Fig.1 Pin connections - top view

#### **FEATURES**

- Direct Segment Drive Non-Multiplexed

- 5V Supply

- Blanking Input

- Leading Zero Suppressed

- Minimum Segment Pattern per Character

- 20 mA Drive per Segment

- 5-Bit Binary Input

Fig.3 Character representation

Fig.4 Block diagram

#### CT2200

#### ELECTRICAL CHARACTERISTICS (see Fig.5)

## Test conditions (unless otherwise stated): $T_{amb} = +25^{\circ}C$ , $V_{DD} = +5V$

$$T_{amb} = +25^{\circ}C$$

,  $V_{DD} = +5V$

| Characteristic                        | Pin                                            | Pin Value |      |      | Units          | 0              |

|---------------------------------------|------------------------------------------------|-----------|------|------|----------------|----------------|

|                                       | '''                                            | Min.      | Тур. | Max. | Units          | Conditions     |

| Operating voltage range               | 9                                              | 4.5       | 5    | 5.5  | V              |                |

| Supply current                        | 9                                              |           |      | 5    | mA             |                |

| Input voltage high low                | 10-14<br>10-14                                 | 4         |      | 0.8  | v              |                |

| Leakage current                       | 10-14                                          |           |      | 10   | <sub>μ</sub> Α | $V_{IN} = +5V$ |

| Capacitance                           | 10-14                                          |           |      | 10   | pF             |                |

| Output voltage                        | 1, 2,<br>4-6, 8,<br>16, 17,<br>19-21<br>23, 24 |           |      | 1    | v              | Sinking 20mA   |

| Recommended series resistor (if used) |                                                |           | 120  |      | Ω              |                |

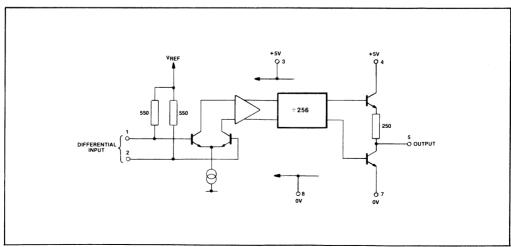

Fig.5 Test circuit and application using load resistors (see also Fig.6)

Fig.6 Minimum component application

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage, V<sub>DD</sub>

+7V

Input or output voltage

+7V

Output current

30 mA

Ambient operating temperature

-10°C to +65°C

Storage temperature

-55°C to +125°C

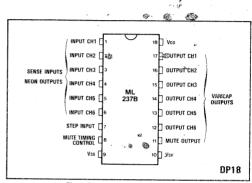

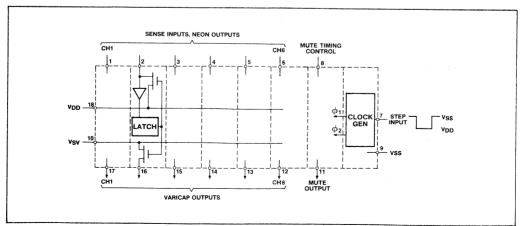

### **ML237B**

#### 6-CHANNEL TOUCH CONTROL INTERFACE

The ML237B is a six-channel sense circuit designed specifically for touch tuning in colour and monochrome television receivers. Using low threshold P-MOS technology, the circuit can be driven directly from two-terminal touch plates - replacing conventional mechanical push-buttons for channel selection. Neons can be used to indicate the selected channel, while the latched output of the ML237B drives the varicap tuner via a bias selection network.

A stepping facility is included whereby the application of a suitable negative-going pulse to the step input causes the selected channel output to advance by one.

#### **FEATURES**

- 6-Channel Capability

- Direct Neon Drive

- Low Impedance Drive to Varicap

- Uses 33V Varicap Supply

- Remote Control Stepping Facility

- Sound Muting During Selection

- Selected Channel 1 on Power-up

- Channels Are Selected With a Negative (or Earth) Input

Fig.1 Pin connections - top view

#### **ABSOLUTE MAXIMUM RATINGS**

Ambient operating temperature -10° C to +65° C Storage temperature -10° C to +85° C Supply, Vss-Vpd 36V Varicap voltage Vsv Vss +0.3V

Fig.2 Functional block diagram

#### ML237B

#### **ELECTRICAL CHARACTERISTICS**

#### Test Conditions (unless otherwise stated):

$$T_{amb} = +25$$

°C,  $V_{DD} = 0$ ,  $V_{SS} = V_{SV} = 30V$  to  $36V$

| Characteristic                    |           | Value |        | Units | Conditions             |  |

|-----------------------------------|-----------|-------|--------|-------|------------------------|--|

| Characteristic                    | Min. Typ. |       | Max.   | Units | Conditions             |  |

| Input current                     |           |       | 1      | μΑ    | Vin = Vss              |  |

| Output leakage                    | 1         |       | 1      | μΑ    | $V_{OUT} = 0$          |  |

| Mute switch O/P leakage           |           |       | 10     | μΑ    | V <sub>OUT</sub> = 0   |  |

| Supply current                    |           | 5     | 8      | mA    | "                      |  |

| R <sub>ON</sub> of varicap switch | 1         | 50    | 100    | Ω     | louτ = 10mA            |  |

| Step pulse width                  | 0.2       |       |        | ms    | >.05Tm                 |  |

| Neon switch output current        |           |       | 2      | mA    |                        |  |

| Mute switch R <sub>ON</sub>       |           | 100   | 200    | Ω     | louτ = 5mA             |  |

| Input threshold                   | 0.4       | 0.5   | 0.6    | Vss   |                        |  |

| Step input current                | 10        |       | 1000   | μΑ    | VIN = 0                |  |

| Mute period                       |           | 400   |        | ms    | $C_{M} = 0.68 \ \mu F$ |  |

| Step pulse level                  | 0         |       | Vss 29 | V     |                        |  |

#### NOTES

The mute timing can be increased by using a higher value of capacitor  $(C_{M})$

Touch plate selection:

MUTE VSS OUTPUT VDD

$Tm \simeq Cm \times 0.6ms/nF$

If the channels are selecting by stepping then the mute output is extended by the clock pulse width T<sub>S</sub>

Stepping selection:

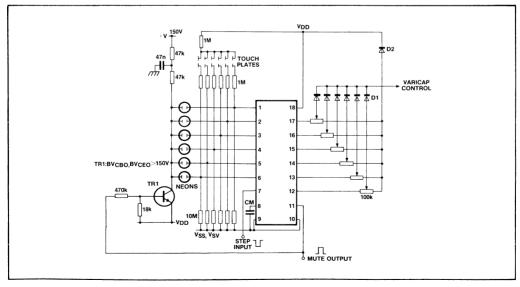

Fig. 3 Typical applications using neons as channel indicators

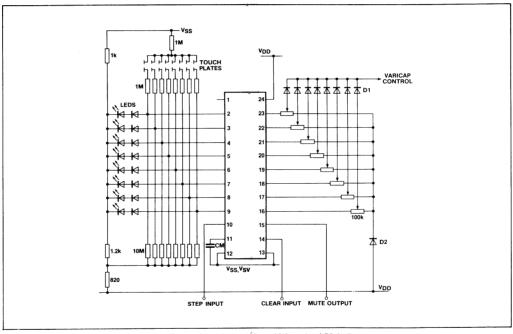

### **ML238B**

#### **8-CHANNEL TOUCH CONTROL INTERFACE**

The ML238B is an eight channel sense circuit designed specifically for touch tuning in colour and monochrome television receivers. Using low threshold P-MOS technology, the circuit can be driven directly from two-terminal touch plates - replacing conventional mechanical push-buttons for channel selection. Neons or LEDs may be used to indicate the selected channel, while the latched output of the ML238B drives the varicap tuner via a bias selection network.

A stepping facility is included whereby the application of a suitable negative-going pulse to the step input causes the selected channel to advance by one.

#### **FEATURES**

- 8-Channel Capability

- Direct Neon Drive

- Direct Neon or LED Drive

- Low Impedance Drive to Varicap

- Uses 33V Varicap Supply

- Remote Control Stepping Facility

- Sound Muting During Selection

- Selects Channel 1 on Power-up

- A Negative Pulse on Clear Resets to Channel 1

Fig.1 Pin connections - top view

#### **ABSOLUTE MAXIMUM RATINGS**

Fig.2 Functional block diagram

#### **ELECTRICAL CHARACTERISTICS**

#### Test conditions (unless otherwise stated):

$T_{amb} = +25$ °C,  $V_{DD} = 0$ ,  $V_{SS} = V_{SV} = 30$ V to 36V

|                            |         | Value |          |          | 0 11:1            |  |

|----------------------------|---------|-------|----------|----------|-------------------|--|

| Characteristic             | Min Typ |       | Max      | Units    | Conditions        |  |

| Output leakage             |         |       | 1        | μA       | $V_{out} = 0$     |  |

| Supply current             |         | 6     | 9        | mA       |                   |  |

| Input current              |         |       | 1 1      | μA       | $V_{in} = 0V$     |  |

| Ron of varicap switch      |         | 50    | 100      | Ω        | louτ = 10mA       |  |

| Ron of indicator switch    |         | 180   | 300      | Ω        | Тоит = 10mA       |  |

| I/P threshold              | 0.4     | 0.5   | 0.6      | $V_{SS}$ |                   |  |

| Step pulse level           | 0       |       | Vss - 29 | . V      |                   |  |

| Ts step pulse width        | 0.2     |       |          | ms       | >.0 5 Tm          |  |

| Clear pulse level          | 0       |       | Vss -29  | V        |                   |  |

| Clear pulse width          | 0.2     |       |          | ms       |                   |  |

| Ron of mute switch         |         | 100   | 200      | Ω        | lout = 5mA        |  |

| T <sub>m</sub> mute timing |         | 400   |          | ms       | $Cm = 0.68 \mu F$ |  |

| Step I/P current           | 10      |       | 1000     | μA       | $V_{in} = 0$      |  |

| Mute O/P leakage           |         |       | 10       | μA       | Vout = 0          |  |

#### MOTES

The mute timing can be increased by using a higher value of capacitor  $(C_m)$  (See Fig. 4).

Touch plate selection: MuTE Vss  $T_m \simeq C_m \times 0.6 ms/nF$

If the channels are selecting by stepping then the mute output is extended by the clock pulse width  $T_{\boldsymbol{s}}$ .

Stepping selection:

| Stepping selection | Steppin

The clear I/P should be left open circuit when not in use.

Fig. 3 Typical applications using neons as channel indications

#### **APPLICATION NOTES**

#### Application using LEDs as channel indicators

In applications where the use of mains is not desired channel selection can be made by using the +30 V Vss supply as a compromise but at the expense of reduced input sensitivity. In this case LEDs can be used as channel indicators.

The 1.2k  $\Omega$  and 820 $\Omega$  resistors limit the LED current to 10mA, whilst the diode ensures less than 1 $\mu$ A leakage when the LED is reverse biased. It is desirable to have a 1M $\Omega$  resistor between the touch plates and the input as a safeguard against static.

On selection of a channel, the potential divider chain comprising the  $1M\Omega$  resistor, the finger resistance and the  $10M\Omega$  resistor sets the threshold voltage on the input pin. When the channel is selected the IC provides a current source to the LED.

Fig. 4 Low voltage, improved sensitivity using LED indicators

#### ML238B

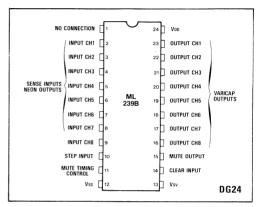

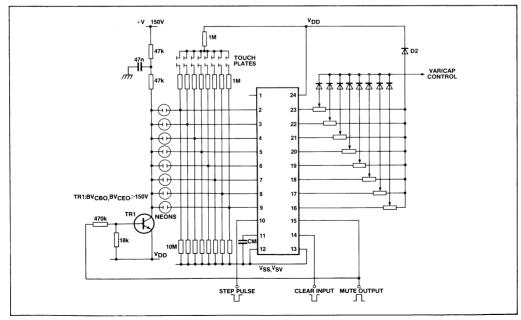

### **ML239B**

#### 8 - CHANNEL TOUCH CONTROL INTERFACE

The ML239B is an eight channel sense circuit designed specifically for touch tuning in colour and monochrome television receivers. Using low threshold P-MOS technology, the circuit can be driven directly from two-terminal touch plates — replacing conventional mechanical push-buttons for channel selection. Neons can be used to indicate the selected channel, while the latched output of the ML239B drives the varicap tuner via a bias selection network.

A stepping facility is included whereby the application of a suitable negative-going pulse to the step input causes the selected channel output to advance by one.

#### **FEATURES**

- 8-Channel Capability

- Direct Neon Drive

- Low Impedance Drive to Varicap

- Uses 33V Varicap Supply

- Remote Control Stepping Facility

- Sound Muting During Selection

- Selects Channel 1 on Power-up

- A Negative Pulse on Clear Resets to Channel 1

- Channels are Selected with a Negative (or Earth) Input

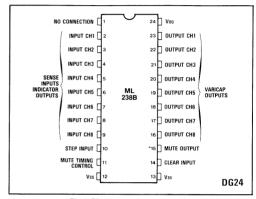

Fig.1 Pin connections - top view

#### ABSOLUTE MAXIMUM RATINGS

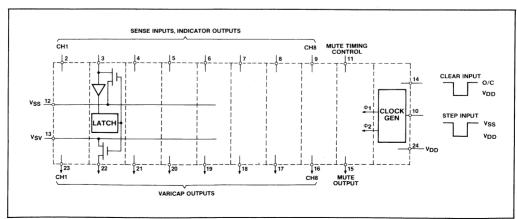

Fig.2 Functional block diagram

#### **ELECTRICAL CHARACTERISTICS**

## Test Conditions (unless otherwise stated): $T_{amb} = +25^{\circ}C,\, V_{DD} = 0,\, V_{SS} = V_{SV} = 30V \text{ to } 36V$

| Characteristic                                                                                                                                                                                                                        |                  | Value                        |                                    | Units                                                         | Conditions                                                                                                                                                                                                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Characteristic                                                                                                                                                                                                                        | Min Typ          |                              | Max                                | Onits                                                         | Conditions                                                                                                                                                                                                                                                                                      |  |

| Step, clear pulse level Input current Output leakage Mute switch O/P leakage Supply current Ron of varicap switch Clear step pulse width Neon switch output current Ron of mute switch Input threshold Step input current Mute period | 0.2<br>0.4<br>10 | 6<br>50<br>100<br>0.5<br>400 | Vss -29 1 1 10 9 1000  2 200 0.6 1 | V  µA  µA  µA  mA  Ω  ms  MA  Q  ms  mA  MA  Noss  mA  MA  ms | $\begin{array}{l} \text{V}_{\text{IN}} = \text{V}_{\text{SS}} \\ \text{V}_{\text{OUT}} = 0 \\ \text{V}_{\text{OUT}} = 0 \\ \text{Iout} = 10 \text{mA} \\ \geq .05 \text{Tm} \\ \\ \text{Iout} = 5 \text{mA} \\ \text{V}_{\text{IN}} = 0 \\ \text{C}_{\text{M}} = 0.68  \mu\text{F} \end{array}$ |  |

The mute timing can be increased by using a higher value of capacitor (C<sub>m</sub>)

$T_m \simeq C_m \times 0.6 ms/nF$ Touch plate selection:

If the channels are selecting by stepping then the mute output is extended by the clock pulse width Ts.

Stepping selection:

The clear I/P should be left open circuit when not in use.

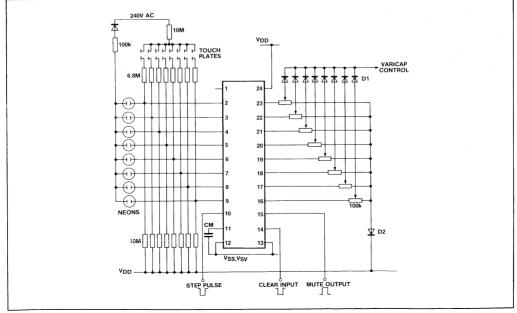

Fig. 3 Typical applications using neons as channel indications

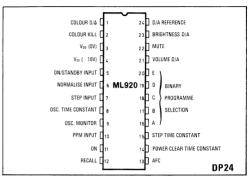

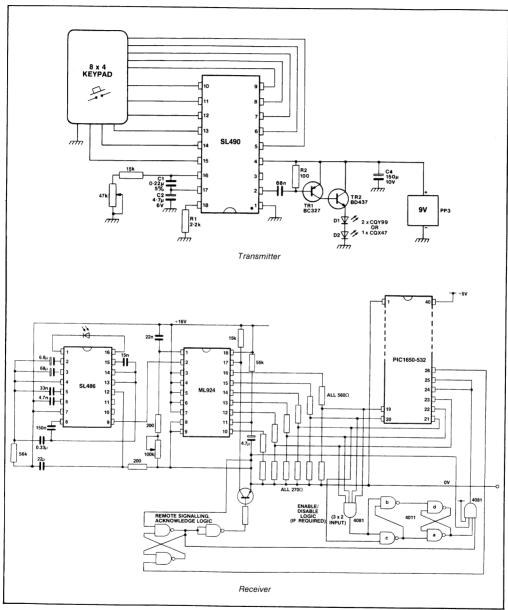

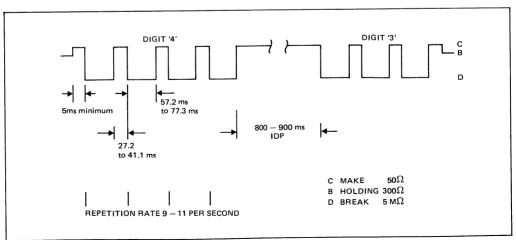

## ML920 REMOTE CONTROL RECEIVER

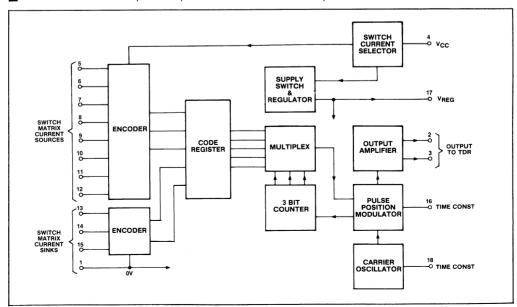

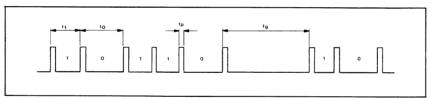

Plessey Semiconductors have developed and produced a range of monolithic integrated circuits which give a wide variety of remote control facilities. As well as ultrasonic or infra red transmission, cable, radio or telephone links may also be utilised. Pulse position modulation (PPM) is used with or without carrier and automatic error detection is also incorporated. Although initially designed with TV remote control in mind the devices may equally easily be applied for use in radios, tuners, tape and record decks, lamps and lighting, toys and models, industrial control and monitoring.

The ML920 decodes the PPM signal received from the SL490 transmitter. After error checking the received code may condition a 20 programme memory or one of three D/A converters.

#### QUICK REFERENCE DATA

- Power supply: 16V 14mA

- Demodulation: Pulse position with time window checking by on-chip oscillator

- Decoder: 5 bit with successive codeword comparison

- Programme: Latched 5 bit binary, 20 programmes

- Analogue controls: 3 static current mirror converters,

32 step with normalise level

- Other outputs: On, Recall Display, AFC, Mute, Colour Kill, Oscillator Monitor

- Local inputs: On/Standby, Step, Normalise

Fig.1 Pin connections (top view)

#### **FEATURES**

- Accepts 5 Bit PPM

- All Timing From On-Chip Oscillator

- Incorporates Error Protection

- Easily Used with Ultrasonic or Infra-Red System

- Up to 20 Programmes with Latched Binary Output

- 3 D/A Outputs with Normalise Level at % of Max.

- Automatic Power-On Reset and Normalise

- Many Other Facilities, AFC, Mute, Colour Kill, Recall etc.

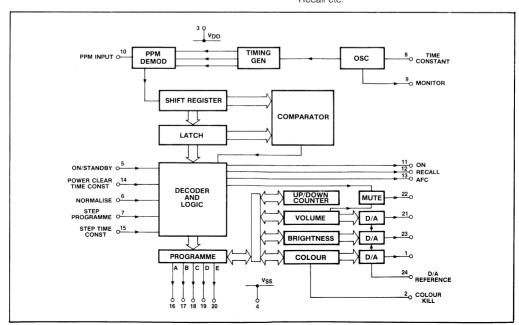

Fig. 2 ML920 remote control receiver block diagram

#### ML920

#### **ELECTRICAL CHARACTERISTICS (see Fig. 3)**

#

|                                                                                                                                                                                                                                                                                                                                      |                                                                                            |                                                                                            | Value                    |                                                                                                                                                  |                                                                      |                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristics                                                                                                                                                                                                                                                                                                                      | Pin                                                                                        | Min.                                                                                       | Тур.                     | Max.                                                                                                                                             | Units                                                                | Conditions                                                                                                                                                                                                                                                   |

| Supply voltage Supply current Input logic level high low Output logic level high low Analogue output current range (pins 1, 21, 23) Analogue step size D/A reference, Irer Oscillator timing Power clear time constant Step time constant Monitor output 'high' 'low' PPM input level high PPM input level low PPM input pulse width | 3<br>5, 6, 7,<br>2, 11-13, 16-20, 22<br>1, 21, 23<br>1, 21, 23<br>24<br>9<br>14<br>15<br>9 | 14 -1 V <sub>DD</sub> -1 V <sub>DD</sub> 0 0 -250  -1 V <sub>DD</sub> -1 V <sub>DD</sub> 1 | 8<br>-345<br>1.5k<br>400 | 18<br>14<br>0<br>V <sub>DD</sub> +3.5<br>0<br>V <sub>DD</sub> +0.5<br>$\frac{31}{8}$ $\frac{1}{4}$ $-455$ $0$ $V_{DD} +0.5$ $0$ $-6$ $22T_{osc}$ | V mA V V V V V V IREF µA HZ ms S V V V V V V V V V V V V V V V V V V | $50k \text{ to } V_{DD}$ $50k \text{ to } V_{DD}$ $3.9k \text{ to } V_{DD}$ $V_{out} < V_{DD} + 5V$ $33k \text{ to } V_{DD}$ $C = 22n, R = 100k \text{ See note 1}$ $C = 4.7\mu R = 100k$ $C = 470n R = 3.3M$ Internal load provided $T = \frac{1}{f_{osc}}$ |

Note 1. Rosc (Pin 8) is 56k-156k $\Omega$ , 2fmon (Pin 9) =  $f_{osc} \simeq \frac{1}{0.15CR} \pm 20\%$

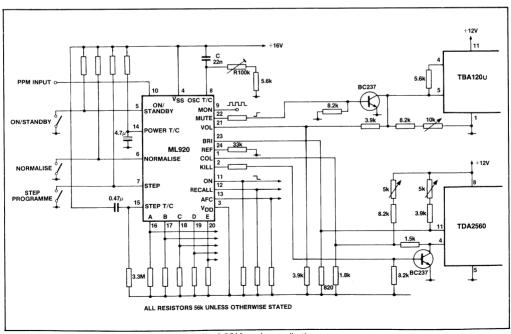

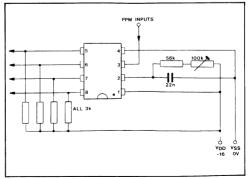

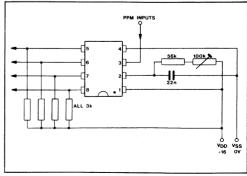

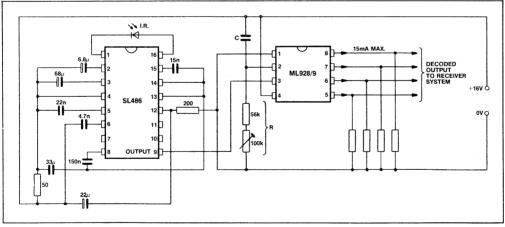

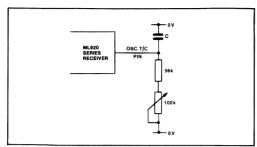

Fig. 3 PPM receiver application

#### PIN FUNCTIONS

Negative Logic: 0 is OV (VSS), 1 is -17V (VDD)

## 1, 21, 23. Colour, Volume, Brightness

These three outputs are from three 5 bit current mirror D/A converters. They are referenced to the current drawn from pin 24,  $l_{\rm ref}$ , and give 32 steps,  $l_{\rm ref}/8$  per step, from 0 to 31/8  $l_{\rm ref}$ . The outputs will be set to 12/8  $l_{\rm ref}$  by the NORMALISE input, the normalise code from the transmitter, or when the ON output goes to a 1.

### 2. Colour kill

This output gives a logic 0 when the COLOUR  $\,\mathrm{D/A}$  output is zero.

#### 3. V<sub>DD</sub>

-17V power supply

## 4. Vss

0V power supply

# 5. On/Standby input

A 1 on this pin will toggle pin 11 (ON O/P), generate RECALL and AFC, normalise VOLUME, BRIGHTNESS and COLOUR, reset MUTE and set channel code 00000.

# 6. Normalise input

A 1 will normalise the VOLUME, BRIGHTNESS and COLOUR outputs. A RECALL signal is generated and MUTE is reset.

#### 7. Channel step

The channel code will step up by 1 as long as this pin is held at logic 1. The time period between steps is defined by an RC constant attached to pin 15. On reaching 20 the next step returns to 1. On output is set to ON, and AFC is generated. If the TV goes from Standby to ON, RECALL is generated and VOLUME, BRIGHTNESS and COLOUR are normalised. If VOLUME is not 0, MUTE is reset.

# 8. Oscillator time constant

An RC time constant is formed for the clock timing by connecting external components, one resistor and one capacitor, to this pin. Adjusted so that period of output on pin 9 is 1/20 of 0 interval of incoming PPM.

# 9. Oscillator monitor

This output is a division of two of the oscillator, and and is available for testing and setting purpose.

# 10. PPM I/P

The output of the front end amplifier is connected here such that the signal is in the form of positive pulses separated by time periods whose length define the data. With no signal, PPM input is at a low level.

# 11. On O/P

Open drain output. Logic 1 denotes TV set ON: Logic 0 TV set standby. Set to 1 when channel number changes. Set to 0 by power clear or by transmitter selected Standby. Toggle to opposite state by manual ON/STANDBY control.

# 12. Recall O/P

Open drain output. A 1 may be used to trigger an on-screen display. A static output is generated by the manual controls ON/STANDBY and NORMALISE.

A pulse is generated by any channel change if the circuit switches to ON at the time, and by RECALL and NORMALISE commands from the transmitter.

#### 13. AFC O/P

Open drain output. Logic 1 can inhibit the tuner AFC. A static output is generated bymanual ON/STANDBY control. A pulse is generated by any channel number change.

# 14. Power clear

A capacitor and resistor connected here define the time delay for the power clear circuit, which normalises all D–A outputs etc.

## 15. Channel step time constant

An R-C time constant defines the time period between increments of the channel number when stepping.

#### 16-20. Channel outputs

5 Outputs encode 20 channel numbers in binary code

EDCBA Channel 1 is 0 0 0 0 0

Channel 20 is 1 0 0 1 1 E is first and A is last in the PPM pulse train.

Channel 1 is set when ON goes to a 1

# 21. Volume.

See Pin 1

# 22. Mute O/P

This will change state (toggle) on reception of a mute command and VOLUME O/P is zero MUTE O/P is held at 0.

## 23. Brightness

See Pin 1

# 24. D/A Reference

A current drain I<sub>ref</sub>, set by a single external resistor will set the nominal step of the D/A outputs to I<sub>ref</sub>/8.

| Transmitter code                                                                                                                                                                                                         | Function                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDCBA                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                               |

| EDCBA  00000 00001 00001 00011 00100 00101 00110 00111 01000 01001 01101 01100 01101 01110 01111 10000 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 11010 | Programme 1 Programme 2 Programme 3 Programme 4 Programme 5 Programme 6 Programme 7 Programme 8 Programme 9 Programme 10 Programme 11 Programme 12 Programme 13 Programme 14 Programme 15 Programme 16 Programme 17 Programme 17 Programme 17 Programme 18 Programme 19 Programme 20 Colour + |

| 10100<br>10101<br>10110<br>10111<br>11000<br>11001<br>11010<br>11011<br>11100<br>11101<br>11110                                                                                                                          | Colour + Programme Step + Volume + Brightness + Standby Mute Recall Normalise Colour - Programme Step - Volume - Brightness -                                                                                                                                                                 |

Table 1 Basic 32 command set

# ABSOLUTE MAXIMUM RATINGS $(V_{ss} = 0V)$ .

| Supply Voltage V <sub>DD</sub>           | +0.3V to $-25V$ |

|------------------------------------------|-----------------|

| Voltage at any input                     | +0.3V to $-25V$ |

| Operating voltage range, V <sub>DD</sub> | -14V to -18V    |

| Maximum power dissipation                | 600mW           |

| Operating temperature range              | -10°C to +65°C  |

| Storage temperature range                | -55°C to +125°C |

# **REMOTE CONTROL RECEIVER**

Plessey Semiconductors have developed and produced a range of monolithic integrated circuits which give a wide variety of remote control facilities. As well as ultrasonic or infra red transmission, cable, radio or telephone links may also be utilised. Pulse position modulation (PPM) is used with or without carrier and automatic error detection is also incorporated. Although initially designed with TV remote control in mind the devices may equally easily be applied for use in radios, tuners, tape and record decks, lamps and lighting, toys and models, industrial control and monitoring.

The ML922 decodes the PPM signal received from the SL490 transmitter. After error checking the received code may condition a 10 programme memory or one of three D/A converters.

The receiver timing may be set by adjusting the oscillator time constant to give 40 periods at pin 6 equal to a 0 interval on the received PPM input.

# **FEATURES**

- Accepts 5 Bit PPM

- All Timing From On-Chip Oscillator

- Incorporates Error Protection

- Easily Used With Ultrasonic or Infrared System

- Up to 10 Programmes With Latched Binary Output

- Automatic Power-On Reset and Normalise

- Many Other Facilities, AFC, Mute, Etc.

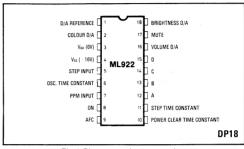

Fig.1 Pin connections - top view

# QUICK REFERENCE DATA

- Power supply: 16V 14mA

- Demodulation: Pulse position with time window checking by on-chip oscillator

- Decoder: 5 bit with successive codeword comparison

- Programme: Latched 4 bit binary,10 programmes

- Other outputs: On, AFC, Mute

- Local inputs: Programme step

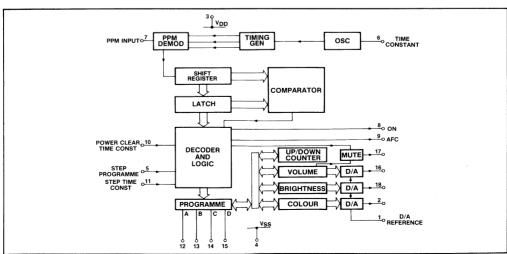

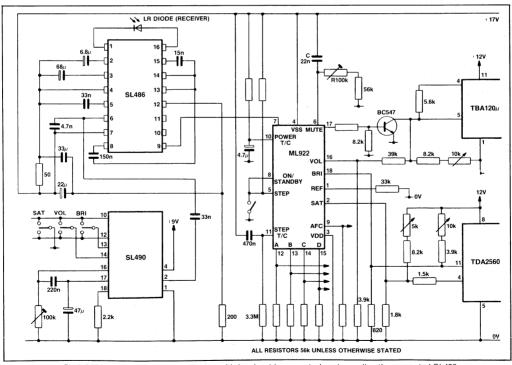

Fig. 2 ML922 remote control receiver block diagram

# **ELECTRICAL CHARACTERISTICS (see Fig. 3)**

|                         |                 | Value    |      |                                                                                                                |                  |                              |

|-------------------------|-----------------|----------|------|----------------------------------------------------------------------------------------------------------------|------------------|------------------------------|

| Characteristic          | Pin             | Min.     | Тур. | Max.                                                                                                           | Unit             | Conditions                   |

| Supply voltage          | 3               | 14       |      | 18                                                                                                             | V                |                              |

| Supply current          | 3<br>3<br>5     |          | 8    | 14                                                                                                             | mΑ               |                              |

| Input logic level high  | 5               | -1       |      | 0                                                                                                              | V                |                              |

| low                     |                 | VDD      |      | VDD + 3.5                                                                                                      | V                |                              |

| Output logic level high | 8, 9, 12-15, 17 | -1       |      | 0                                                                                                              | V                | 50k to VDD                   |

| low                     |                 | VDD      |      | V <sub>DD</sub> + 0.5                                                                                          | V                | 50k to V <sub>DD</sub>       |

| Analogue output         |                 |          |      | 31<br>8                                                                                                        |                  |                              |

| current range           | 2, 16, 18       | 0        |      | 8                                                                                                              | I <sub>ref</sub> | 3.9k to VDD                  |

| Analogue step size      | 2, 16, 18       | 0        | 1 8  | 1/4                                                                                                            | Iref             | $V_{out} < V_{DD} + 5V$      |

| D/A reference, IREF     | 1               | -250     | _345 | -455                                                                                                           | μA               | 33k to Vpp                   |

| Oscillator timing       | 6               |          | 3    |                                                                                                                | kHz              | C = 22n, R = 100k See note 1 |

| Power clear time        | 10              |          | 400  | la de la companya de | ms               | $C = 4.7 \mu R = 100 k$      |

| constant                |                 |          |      |                                                                                                                |                  | · ·                          |

| Step time constant      | 11              |          | 2    |                                                                                                                | s                | C = 470n R = 3.3M            |

| PPM input level high    | 7               | -1       |      | 0                                                                                                              | V                |                              |

| PPM input level low     | 7               | $V_{DD}$ |      | -6                                                                                                             | V                |                              |

| PPM input pulse width   | .7              | 1        |      | 22Tosc                                                                                                         | μs               |                              |

Note 1. R<sub>osc.</sub> (pin 6) is 56k-156k  $\Omega$ . f<sub>osc.</sub>  $\simeq \frac{1}{0.15 \text{CR}} \text{I}^{\pm}20\%$

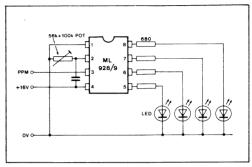

Fig.3 PPM infra-red receiver application with local up/down controls using a directly connected SL490

Note: Pin descriptions same as ML920.

| Transmitter code | Function          |

|------------------|-------------------|

| EDCBA            |                   |

| 0000X            | Programme 1       |

| 0001X            | Programme 2       |

| 0010X            | Programme 3       |

| 0011X            | Programme 4       |

| 0100X            | Programme 5       |

| 0101X            | Programme 6       |

| 0110X            | Programme 7       |

| 0111X            | Programme 8       |

| 1000X            | Programme 9       |

| 1001X            | Programme 10      |

| 10100            | Colour +          |

| 10101            | Programme Step +  |

| 10110            | Volume +          |

| 10111            | Brightness +      |

| 11000            | Standby           |

| 11001            | Mute (Analogue 2) |

| 11011            | Normalise         |

| 11100            | Colour —          |

| 11101            | Programme Step —  |

| 11110            | Volume —          |

| 11111            | Brightness —      |

Table 1 Basic 21 command set for ML922

# ABSOLUTE MAXIMUM RATINGS (Vss=0V).

| 0 1 1/1: 1/                 | 0.014           |

|-----------------------------|-----------------|

| Supply Voltage $V_{DD}$     | +0.3V to −25V   |

| Voltage at any input        | +0.3V to $-25V$ |

| Maximum power dissipation   | 600mW           |

| Operating temperature range | -10°C to +65°C  |

| Storage temperature range   | -55°C to +125°C |

# **ADVANCE INFORMATION**

Advance information is issued to advise Customers of new additions to the Plessey Semiconductors range which, nevertheless, still have 'pre-production' status. Details given may, therefore, change without notice although we would expect this performance data to be representative of 'tull production' status product in most cases. Please contact your local Plessey Semiconductors Sales Office for details of current status.

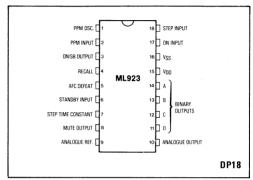

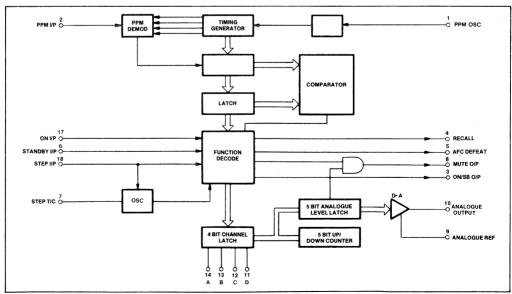

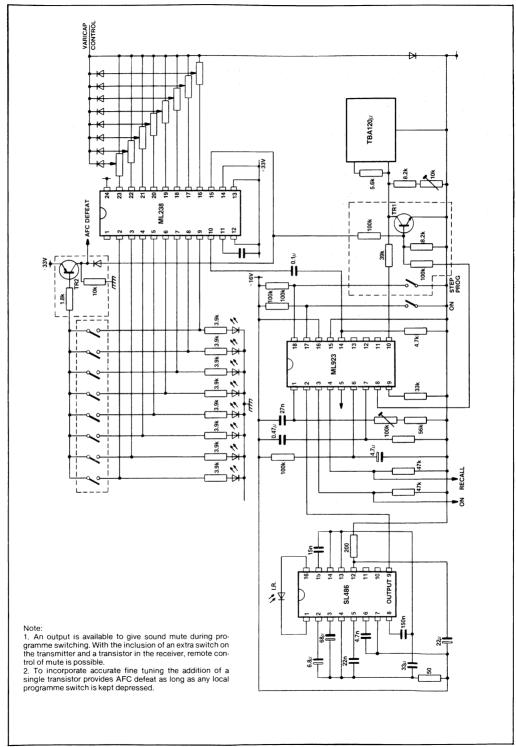

# **ML923**

# REMOTE CONTROL RECEIVER

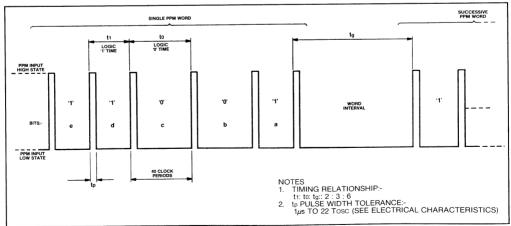

The ML923 is an MOS/LSI monolithic integrated circuit for use as a receiver of remote control signals for television control. It accepts 24 of the 32 codes transmitted by the SL490 transmitter circuit in the Pulse Position Modulation (PPM) method of coding.

## **FEATURES**

- 16 Channel Selection Codes

- Single Analogue Output

- Mute Output (Toggle)

- On-set Controls Channel Step, ON, Reset

- Normalise to 3 of Max Output on Analogue Output

- Outputs Provide Control of ON/STANDBY, Analogue Mute, and AFC Defeat

- Choice of Power-Up Function:

- a) Power Up to Standby State, Switch to ON State by Local or Remote Command and STANDBY by Remote Command.

- b) Power Up to ON State, Switch OFF with Solenoid Operated Mains Switch by Local or Remote Command.

Fig.1 Pin connections (top view)

Fig.2 ML923 block diagram

# **ELECTRICAL CHARACTERISTICS**

# Test conditions (unless otherwise stated):

$T_{amb} = +25^{\circ}C$ ,  $V_{SS} = 0V$ ,  $V_{DD} = -16V$

| Characteristics                                      | Pin Value    |                 |      |                       |       |                                            |

|------------------------------------------------------|--------------|-----------------|------|-----------------------|-------|--------------------------------------------|

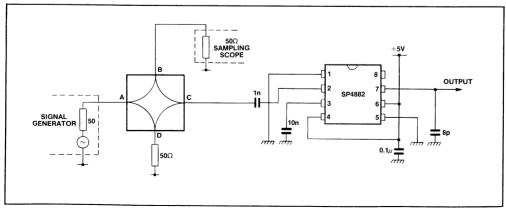

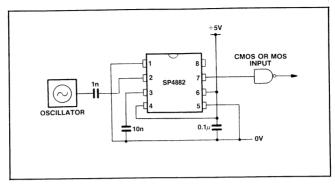

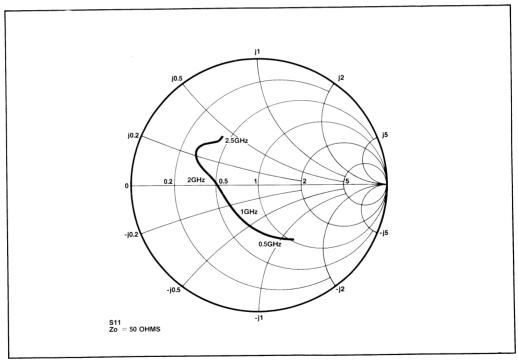

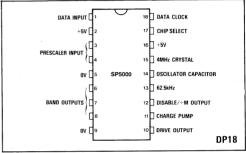

| Characteristics                                      | Pin          | Min.            | Тур. | Max.                  | Units | Conditions                                 |